Генератор модулів фільтрів для ПЛІС

Моделювання та інформаційні технології. Зб. наук. праць. Ін-т проблем моделювання в енергетиці ім. Г.Е. Пухова. НАНУ. -2002. -Вип.12. -С. 13-18

В.ВАСИЛЕНКО, інж., O. КЛИМЕНКО, студ. Л.М. ЛОГІНОВА, мол.наук.сп., А.М. СЕРГІЄНКО канд.техн.наук, ст.наук.сп.

ГЕНЕРАТОР МОДЕЛЕЙ ФІЛЬТРІВ ДЛЯ ПЛІС.

Запропоновано спосіб виконання множення в програмованих логічних інтегральних схемах (ПЛІС) на основі таблиць кратних множених, що забезпечує зменшення апаратурних витрат і підвищення швидкодії. На основі цього способа розроблена методика синтезу структур цифрових фільтрів зі скінченною імпульсною характеристикою (СІХ). Методика реалізована у вигляді програми, яка генерує моделі СІХ-фільтрів, які описані мовою VHDL і призначені для реалізації в ПЛІС.

A method for multiplication in FPGA is proposed which is based on the tables of partial product sums. This method is implemented in the software tool for

the FIR filter structure generation. The generated filter structures are described on VHDL, and have minimized both hardware volume and clock period.

Вступ. Фільтри зі скінченною імпульсною характеристикою (СІХ – фільтри) широко вікористовуються в системах цифрової обробки сигналів, завдяки їхній високій швидкодії, лінійній фазовій характеристиці, простим процедурам обчислення характеристик. Реалізація СІХ-фільтрів на ПЛІС має ряд переваг, таких як висока продуктивність, малі апаратні витрати, можливість швидкого перенастроювання і висока якість фільтрування завдяки повній адаптації реалізованої структури до алгоритму фільтрації.

Однією з основ сучасної технології розробки систем на кристалі є використання в проектах обчислювальних модулів з заданими параметрами. Наприклад, блоків ОЗП, що генеруються за допомогою спеціальної програми – генератора модулів. Генератор модулів СІХ – фільтрів може спростити і прискорити розробку проектів, де необхідні СІХ – фільтри з заданими ампулітудо-частотною характеристикою і відношенням сигнал-шум. Генератор СІХ – фільтрів з пакету Xilinx FIR СoreGen™ став широко відомим завдяки високій швидкодії та невеликим апаратним витратам генерованих ним фільтрів [1]. Цей генератор генерує модулі фільтрів, які представлені за допомогою схеми на логічному рівні в стандартному форматі EDIF. Це приводить до того, що діапазон настроюваних параметрів є невеликим і згенеровані модулі знаходять використання в обмеженій множині мікросхем ПЛІС.

В статті описані особливості розробки нового генератора модулів СІХ – фільтрів, що генерує фільтри, описані мовою VHDL, які мають підвищену швидкодію, мінімізовані апаратні витрати, широкий діапазон зміни параметрів довжини характеристики, розрядності даних і коефіцієнтів, і які можуть бути реалізовані в будь-якій серії ПЛІС, або замовленій НВІС.

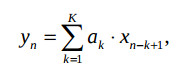

Методи множення на коефіцієнти, які застосовуються в ПЛІС. Обчислення СІХ -фільтра, або згортка полягає в знаходженні наступної суми добутків

де xn-k+1 – вхідні дані, ak-коефіцієнти імпульсної характеристики , K – довжина імпульсної характериститки, yn – вихідні результати з індексом n. Щоб одержати один результуючий відлік фільтр повинен зробити близько K множень і додавань. Тому операція згортки є досить трудомістською.

ПЛІС перших поколінь не були розраховані для високопродуктивних обчислень, таких як згортка. Тому раніше блоки множення програмувались як система логічних рівнянь або матриця елементів “І” з деревом суматорів. Тільки в останній час, коли ПЛІС почали широко застосовувати в цифровій обробці сигналів, в нових серіях ПЛІС почали додаватись окремі блоки множення.

В багатьох проектах в процедурі згортки множення виконується на сталий коефіцієнт. Тому застосування комбінаційних схем множення з такою метою є досить збитковим. Крім того, число блоків множення в нових серіях ПЛІС, як в Xilinx VirtexІІ™, є обмеженим і часто недостатнім для вирішення багатьох задач. Отже, різними авторами було запропоновано ряд способів, що використовують властивості блоків множення на сталу. Наприклад, якщо взяти до уваги, що середнє число одиничних бітів в m – бітовій константі дорівнює m/2, то можна розробити блок множення на сталу, який має дерево з m/2-1 суматорів, що в 2 рази менше, ніж у звичайного блока множення. Слід відмітити, що існує ряд методів синтезу імпульсної характеристики фільтрів, які мінімізують число одиничних розрядів в коеффіцієнтах до 1-3. Але такими методами неможливо розробити високоякісні фільтри з довільною характеристикою.

В роботі [2] було запропоновано метод одержання суми добутків, який називається розподілена арифметика. Метод полягає в збереженні в ПЗП 2K комбінацій сум до K коефіцієнтів. Якщо i-й зріз бітів вхідного набору даних подається на адресний вхід такого ПЗП, то з нього буде зчитана відповідна сума часткових добутків. Результуюча сума добутків одержується, коли m таких сум буде додано до числа в акумуляторі результату з відповідним зсувом розрядів.

Такий спосіб був запропонований в роботі [3] як спосіб одержання суми добутків в ПЛІС. Згідно цьому способу 4-входова логічна таблиця (LUT) програмується як швидкісний 16-бітовий ПЗП. Цей спосіб широко використовується як в багатьох застосуваннях цифрової обробки сигналів, так і в генераторі Xilinx FIR СoreGen [1]. З метою одержання високої швидкодії всі суми часткових добутків для i–тих бітів коефіцієнтів обчислюються паралельно. Тому такі схеми фільтрів звичайно називають фільтрами з паралельною розподіленою арифметикою (parallel distributed arithmetic -PDA). Недоліком цього способу є великий об’єм ПЗП якщо число коефіцієнтів K фільтра більше, ніж 8,…,12. Для зменшення цього недоліка структуру фільтра ділять на блоки, кожен з яких обчислює суму K=4 або 5 добутків.

В роботі [4] опубліковано інший ефективний спосіб множення в ПЛІС. Він оснований на використанні ПЗП, в i-й комірці якого зберігається коефіцієнт a, який помножений на число i. Тому ПЗП з об’ємом 2m представляє собою блок множення на сталу для m-бітових даних. Далі детально описується такий самий спосіб, але який ще раніше був запропонований в роботі [5].

Коли допустимий об’єм ПЗП надто малий, то вхідні дані розділяються на l вирізок з p розрядів, так що m≤ lp, а результат одержується як сума l часткових добутків. В [5] було показано, що такі блоки множення при реалізації в НВІС є ефективнішими, ніж звичайні блоки множення 16-розрядних даних, якщо сумарний об’єм ПЗП не більший, ніж 4 кілобайта, а оптимальний розмір вирізки розрядів дорівнює p=4. Приклад структури такого блоку множення на сталу для 16-розрядних даних і p=4 показано на рисунку 1.

Така реалізація блоку множення на сталу в ПЛІС має наступний ряд переваг:

• Висока продуктивність. Схема такого блоку може бути реалізована як конвеєр з мінімізованою затримкою у всіх його ступенях. Тому мінімальний період циклу синхронізації дуже короткий і не перевищує затримки одного суматора.

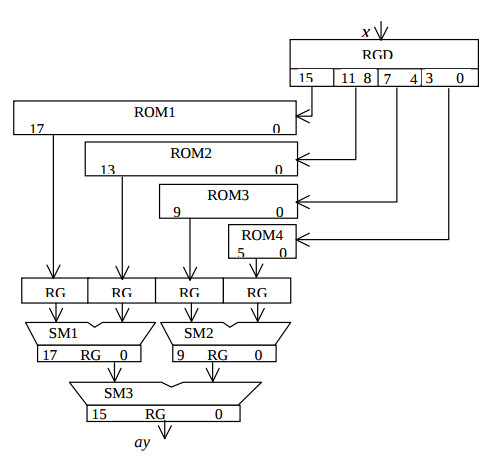

• Зменшений об’єм апаратури. Результуючий об’єм апаратури СІХ-фільтрів не більший або значно менший, ніж об’єм апаратури фільтрів PDA. Це зумовлено наступною причиною. Нехай коефіцієнт a має послідовність j однакових розрядів (одиничних або нульових). Тоді в ПЗП вирізка з j-p+1 розрядів буде зберігати біти, які дорівнюють один одному. Крім того, часто однорозрядні вирізки повторюють стан розрядів адреси. При трансляції в логічну схему компілятор-синтезатор на стадії мінімізації апаратних витрат замінює вирізку з цього ПЗП на генератор константи і підключає деякі вихідні розряди до розрядів адреси. Цей ефект проілюстровано на рисунку 2 для випадку множення на коефіцієнт 0,62573 при р=3. СІХ – фільтри, які звичайно використовуються на практиці, мають більше, ніж 70% коефіцієнтів, які мають більше j=4 однакових старших розрядів і близько 40% коефіцієнтів що мають більше, ніж 7 таких розрядів. Тому, за рахунок мінімізації кодування тільки цих розрядів в ПЗП, результуючий фільтр матиме в 1.1,…,1.6 разів менше апаратних витрат, ніж фільтр типу PDA, в залежності від набору коефіцієнтів фільтра.

• Збільшена еквівалентна розрядність коефіцієнтів. Така властивість пов’язана з тим, що якщо коди коефіцієнтів запам’ятовувати в ПЗП і округляти до m розрядів після множення коефіцієнта a на константу i, а не перед таким множенням, то до молодших розрядів кратних множників додаються кратні відкинуті розряди. Тому еквівалентна розрядність коефіцієнтів в фільтрах може бути оцінена як m-2, де m дорівнює максимальній розрядності ПЗП, яке використовується в даному фільтрі. При тих же умовах розрядність коефіцієнтів в фільтрі типу PDA дорівнює лише m-p.

Генератор СІХ – фільтрів. Розроблено генератор модулів СІХ – фільтрів, які використовують блоки з множенням на ПЗП. Генеровані фільтри мають звичайну структуру, яка включає блок внутрішніх регістрів для конвеєрної затримки вхідних даних і дерево суматорів, яке обчислює суму затриманих і зважених даних. Для підтримки високої продуктивності схема фільтру глибоко конвеєризована.

Розрізняються два типи структур, які називаються фільтрами з несиметричною і симетричною імпульсною характеристикою. В останніх фільтрах використовується властивість однаковості пар коефіцієнтів, завдяки чому вдвічі зменшується кількість блоків множення.

Модулі, що генеруються, описані за допомогою одного VHDL-файла і підходять для реалізації в будь-якій серії ПЛІС. Такий файл може бути cкомпільованим будь-якою синтезуючою програмою в файл схеми на логічному рівні для таких ПЛІС, як Xilinx XC4000, Spartan™, Virtex™, Altera Flex10K ™, Flex20K ™ та інших.

Генератор СІХ – фільтрів розроблено з використанням програми Win32 Delphi з вікном настройки. Також генератор виконано як застосування, яке керується командним рядком. Користувачі можуть змінювати наступні параметри фільтрів:

• набір коефіцієнтів, які можуть задаватись як десяткові, восьмиричні, шіснадцятиричні, двійкові цілі числа або числа в форматі з плаваючою комою;

• розрядність вхідних і вихідних даних від 4 до 24 біт;

• розрядність коефіцієнтів від 4 до 24 біт;

• число коефіцієнтів від 4 до 128;

• фільтри з симетричною, несиметричною або антисиметричною імпульсною характеристиками;

• вхідні дані позитивні або знакові;

• керування швидкістю обчислень за допомогою сигналу дозволу синхросигналу (Clock Enable).

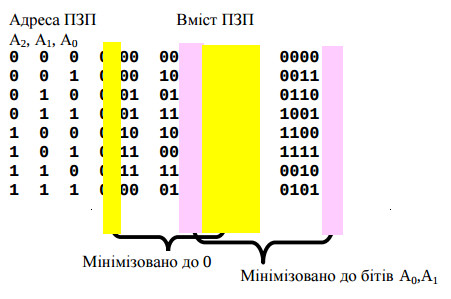

Експериментальні результати. При іспитах генератора було згенеровано набір СІХ – фільтрів, які були занурені в ПЛІС фірми Xilinx за допомогою САПР Foundation 3.1. Для цього були використані набори коефіцієнтів, які зустрічаються на практиці, а саме – коефіцієнти фільтрів нижніх частот і смугових фільтрів з симетричною імпульсною характеристикою з рівнем сигналу в смузі затримання –60,…,-70 дб. Деякі результати для 16 – розрядних даних і коефіцієнтів подані в наступній таблиці. Апаратні витрати приведені в числі еквівалентних КЛБ (ЕКЛБ). Результати для фільтрів, згенерованих за допомогою Xilinx FIR PDA СoreGen, показані для порівняння в нижній смузі таблиці.

| Мікросхема | Число коефіцієнтів, K |

Апаратні витрати, ЕКЛБ |

Максимальна частота дискретизації, MГц |

| VirtexE-8 | 20 | 1022 | 212 |

| VirtexE-8 | 99 | 5151 | 208 |

| XC4000XV-07 | 20 | 1008 | 76 |

| XC4000XV-07 | 20 | 1457 | 50 |

Аналіз таблиці показує, що результуючі структури фільтрів мають високу продуктивність і мінімізовані апаратні витріти. Апаратні витрати практично пропорційні кількості коефіцієнтів, а максимальна частота дискретизації майже не залежить від кількості коефіцієнтів. На рисунку 3. показані порівняльні характеристики названих фільтрів.

Висновки. Розроблено новий генератор моделей СІХ – фільтрів, що синтезуються, який використовує функціональні властивості ПЛІС і мінімізує апаратні витрати результуючого проекту. Він забезпечує розробку сильно конвеєризованих структур з високими тактовими частотами, які можуть досягати значення більше, ніж 200 MГц для сучасних ПЛІС. Заготовки, що генеруються, описані мовою VHDL і представлені одним файлом. Таким чином, можуть бути скомпільовані у будь-яку серію ПЛІС або замовлену НВІС.

ПОСИЛАННЯ

[1] Parallel Distributed Arithmetic FIR filter. Product Specification. Available at http://www.xilinx.com. Feb.8.1988.

[2] Peled A., Liu B. A New Hardware Realization of Digital Filters. IEEE Trans. on Acoustic Signal, Speech Processing, V.ASSP-22, June, 1974.

[3] Mintzer L. FIR filters with the Xilinx FPGA. FPGA’92, ACM/SIGDA Workshop on FPGAs, 1992, pp. 129-134.

[4] Chapman K. Constant Coefficient Multipliers for the XC4000E. Application Note. Available at http://www.xilinx.com. December 11, 1996.

[5] Kаневский Ю.С., Некрасов Б.A., Сергиєнко A.M. К вопросу о разработке высокопроизводительних процессоров БПФ. Управляющие системы и машины, -1986. -№4, -с.60-63.

[6] Kaniewski J., Berezowski R., Gretkowski D., Maslennikov O., Soltan P. Modele VHDL filtrov FIR przeznaczonych do realizaciji w ukladach FPGA. Materialy III Krajowej Konferencji Naukowej “Reprogramowalne uklady cyfrowe”, RUC’2000, Szczecin (Poland), 10-11 Kwietnia 2000. pp.269-276.