A.M. Sergiyenko

# **Computer Architecture**

# Part 1. Central Processing Unit and Peripherals

Kyiv-2016

УДК 004.383 ББК 32.973-018 Рецензенти: А. М. Романкевіч, доктор технічних наук, професор (кафедра спеціализованих обчислювальних систем Національного технічного університету України "КПИ"); В. П. Сімоненко, доктор технічних наук, професор (кафедра обчислювальної техніки Національного технічного університету України "КПИ")

Сергієнко А. М. Архітектура комп'ютерів. Частина 1. Центральний процесорний елемент та периферійні пристрої: Конспект лекцій. Англійською мовою – К.: НТУУ«КПІ», 2016. – 182 с. Розглянуті теоретичні відомості про архітектури сучасних комп'ютерів. Для студентів, аспірантів, викладачів вузів в галузі електроніки, вимірювальної і обчислювальної техніки, зв'язку та захисту інформації. УДК 004.383 ББК 32.973-018

© А. М. Сергієнко, 2016

# CONTENTS

| FOREWORD                                                        | 3   |

|-----------------------------------------------------------------|-----|

| 1. CENTRAL PROCESSING UNIT ARCHITECTURE                         | 5   |

| 1.1 Introduction. Basic definitions and principles of computers | 5   |

| 1.2 Element basis of computers                                  | 33  |

| 1.3. Von Neumann Computer Architecture                          | 44  |

| 1.4. Instruction set of the computer                            | 51  |

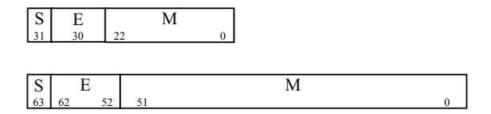

| 1.5. Data formats and operations                                | 56  |

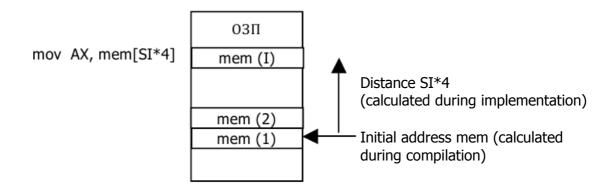

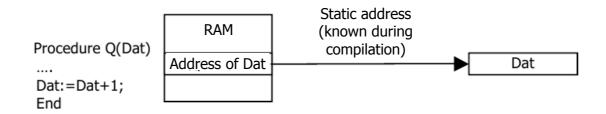

| 1.6. Addressing modes                                           | 69  |

| 1.7 Intel 8051 architecture                                     | 79  |

| 1.8 RISC and CISC processors                                    | 94  |

| 1.9. Interrupt system                                           | 103 |

| 2. PROCESSOR ENVIRONMENT ARCHITECTURE                           | 120 |

| 2.1. Interface basics                                           | 120 |

| 2.2 Memory in computers                                         | 142 |

| 2.3. External storage devices                                   | 156 |

| 2.4 Computer console                                            | 169 |

| 2.5. Structure of a single processor computer                   | 177 |

| BIBLIOGRAPHY                                                    | 180 |

| ANNEX 1                                                         | 182 |

### FOREWORD

The computer architecture is the basic information about a computer, which is necessary both for its design and programming. The development of a new program is the creative process of implementation of a given algorithm on a computer with the specific architecture. The programmer creating a new program must clearly understand what processes and in what order are executed in the computer, which implements that program. Otherwise, the calculation process, which is planned by the programmer, may differ from the computational process, which is really running in a specific computer. As a result, the purpose of the program development may be unachievable.

Every year, more complicated computer architectures are in operation, increasing the degree of inherent parallelism, and the level of information security. At the same time, many programmers understand and percept the computer architecture as unchanged one for decades. On the one hand, this means that programmers can not achieve the most effective implementation of its programs in modern computers without the knowledge of new architectures. On the other hand, the particular organization of computing processes in these computers can lead to inefficient or even incorrect implementation of the programs, which are written for legacy architectures.

Also without architecture knowledge, it is impossible to develop, adjust, and analyse many complex and mission-critical applications that have special requirements for speed, reliability, information protection, energy consumption.

In the "Computer Architecture" discipline the students learn the theoretical information about the architectural elements of modern computers and communication between them, as well as gain the skills for

their use in the selection and programming of microprocessors. Therefore, this discipline is central to the education of specialists in the field of "Information Control Systems and Technologies", "Computer systems and networks".

# **1. CENTRAL PROCESSING UNIT ARCHITECTURE**

#### 1.1 Introduction. Basic definitions and principles of computers

To understand what is architecture, and why it is studied and investigated, we should recall the history of computers.

#### **1.1.1** The history of computers and their architectures

The most significant impetus for the electronic computing machine invention has been a need for improvement of weapons during the Second World War. The problem of calculating the trajectory of shells and bombs was important for the preparation of firing and bombing tables. It was desirable to calculate such a data in real time. To speed up the solution of this problem in 1943 the University of Pennsylvania began to develop the first electronic computer ENIAC (Electronic Numerical Integrator And Computer) by the US Ministry of Defense order. It started its operation in 1946 and worked until 1955.

The Eniac computer had 18,000 electronic lamps and performed multiplication of decimal 10-bit numbers for 2.8 ms. It consisted of several integrators-accumulators, registers, constant and input-output data tables. It performed iterative algorithms for solving differential equations. The programming of such a computer consisted in connection of that registers, accumulators, etc. to the network via data lines in accordance with the algorithm graph.

At the first period, this network was done manually using the wires with connectors, and the switching field, which resembled the telephone exchange. But the algorithm changing process required several days. To

accelerate this process, the special patch panel with the network configuration was invented. Then the algorithm exchange was performed manually by replacing the "programmed" patch panel. So, Eniac was the programmable computer, but both the algorithm set, and data types were very limited.

In 1943 in England, ten copies of the Colossus computer have been developed and manufactured under the leadership of N. Wiener. They were used to decipher German radio messages. According to its principle of operation this computer was the symbolic correlator, which consisted of the 1,500 lamps. However, the structure of it also reflected the structure of the algorithm, and this algorithm was unchanged.

Even earlier — from 1939 to 1942 — D. Atanasof at the State College of Iowa developed the ABC electronic computer. It performed a single algorithm of the linear equation system solution. It has a parallel structure of thirty sequential Arithmetic Logic Units (ALU) with a parallel data storage based on the capacitor drum.

Thus, the first electronic computers were able to perform only one or more similar algorithms that have been encoded in their control devices or interconnect structure. Their ideology was borrowed from the mechanical or electro-mechanical calculators, which were distributed to the middle of the twentieth century. They were very costly. And the computer must be the versatile installation to be much more popular, and effective.

In 1936, Alan Turing has proposed the computational model, in which the arbitrary algorithm is coded as a table in the control unit, and as an initial state of the endless storage tape. This tape was the model of the computer memory. Thus the idea of a computer, that can perform any hypothetical algorithm, was born.

It is believed that the idea of implementing a universal programmable computer first appeared in the US in the Moore Electrical School of the

Pennsylvania University. There was a team of scientists led by von Neumann, which in 1946 drew up a prominent report. In this report, the programable computer design principles were proposed. Among them were the ideas to store both data and program in a single computer memory, to perform the data processing using their binary representation and the apparatus of the Boolean algebra, to fetch the instructions using the instruction counter. Thus, the memory of a computer as the basis of its functionality and versatility was considered.

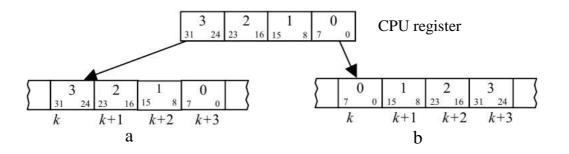

In those days, the computer structure was significantly dependent on the memory design. The register memory based on the vacuum tubes was fast but too expensive and unreliable. The memory based on the mercury acoustic delay lines was very popular. This memory was of the sequential type, and therefore, it determined the sequential, bit-wise processing of the data. The Williams cathode ray tube (CRT) recorded the data bits in the form of pixels on the tube screen and provided the random access to the data. But the volume of such a memory not exceeded thousands of bits.

T. Kilburn, and F. Williams were the first who in June 1948 have calculated the first program in the computer SSEM (Small-Scale Experimental Machine) at Manchester University. It was the world's first stored-program computer, which had successfully demonstrated the practicality of the stored-program approach and the Williams tube memory effectiveness. SSEM was redesigned into the Mark1 computer, which has runned the first program in April 1949.

The Cambridge professor M. Wilkes took over the idea of the Neumann's group and has implemented his first program in the computer EDSAC (Electronic Delay Storage Automatic Computer) in 1949. A year later, the computer EDVAC (Electronic Discrete Variable Automatic Computer) was in the operation in the Moore School. In fact, the Neumann group report was compiled to develop this computer. Both these computers were built on the delay lines. Therefore, they operate synchronously and sequentially, that is, the words are processed bit by bit.

At the same period of time in Kiev, S. A. Lebedev has developed the computer MESM (Malaja Electronno-Stchetnaja Mashina), in which many new ideas have been incorporated. One of them is the parallel ALU data processing (such as was first used in the Whirlwind computer in 1951 in the USA). Second of them is the microprogramming principle (which was published in 1951 and implemented in 1957 by M. Wilks). MESM was running for the first time in 1950 and was put into operation in late 1951. Its successful use for complex calculations in the defense projects has contributed to the emergence, and expanding of the computer industry in the USSR.

The Univac-1 machine, which was produced from 1951 by the Univak affiliate of the Remington company, gave the big push for the commercial distribution of computers. It contained 5000 vacuum tubes and hundreds of delay lines for a thousand 12-digit decimal numbers. The program and data input-output was performed by switches, electric typewriter and a magnetic tape device. In 1953, this company was an early adopter of the random access memory (RAM), based on the magnetic rings. This memory invention improved the computer performance by 50 times.

The increased memory capacity and the random access to it made it possible to introduce the high-level language programming and algorithmic languages like Fortran. As early as 1952 the Remington company offered the use of a first interpreter for the program with the algebraic entry. A female scientist Grace Hopper has developed the first compiler for the Univac computer. She also participated in the development of the Cobol language. Thus, in the 50-s there were first programming languages, and some of them, such as Algol, Fortran, Cobol become standard languages in the 60-ies.

Despite the high cost of the of computers of the first generation (about one million US dollars), their production became commercially viable. Most computer implementations were found in banks and government offices. There they were used for the statistical data processing and the cash payment account. In these areas, the computer can replace hundreds of employees, many times accelerate the solution of problems and, therefore, its use makes a profit. Therefore, the main application of computers of the first generation was the accumulation and processing of large amounts of structured data that were stored on magnetic tape. In past 50-ies, there was a number of computer companies, which competed in speed and price of computers. Thus, in 1959, the DEC (Digital Equipment Corporation) company released the 18-bit computer PDP-1 with the RAM up to 32 Kwords, which cost only 120 thousand US dollars.

The RAM miniaturization and use of the semiconductor devices instead of lamps (second-generation computers) contributed to increased RAM capacity and performance. The concept of the operating system became possible when the RAM capacity achieved several tens of thousands of words in 60-ies. The operating system (OS) provides the users with new capabilities such as virtual memory and time scharing. The study of OS in the early 60-ies in Dartmund College, held by General Electric, has pushed to the processor time scharing. The time-sharing system made it possible for multiple users to manage a single computer at a time. This made it possible to significantly reduce the rent for the use of a computer.

The software in those days was the expensive and necessary complement to each computer. And this was the reason for the disappearance of software incompatible computers in the market. For example, in 1960, the IBM computer Stretch was the high technical achievement, in which the pipelined instruction processing and preliminary analysis of the instruction

queue were introduced. But this and other models of computers have lost the commercial success due to software incompatibilities and other difficulties of working with them.

Therefore, IBM (International Business Machines) in 1961 committed itself to create a unified lineup of computers. Computers need to be really versatile — they are used both for commercial and scientific works, are coupled with a variety of peripheral devices via standard interfaces. In the development of new computers, the leading roles were played by Jim Amdahl and Gerrit Blau, who introduced the name of the computer architecture. The basic idea of the architecture concept was the fact that all members of a computer lineup have to be characterized by the same architectural features: the same instruction set, addressing modes, etc. Due to this, they can implement the same program with the equal results for the original data. To implement the same system of complex instructions in the variety of processors, the microprogramming was introduced in all the computer models.

Simultaneously, six models of computers with an IBM-360 architecture were designed, which were differed among themselves by the cost and speed. Up to 47 different peripheral devices in any configuration could be installed in the sold computers. The cache RAM was first introduced in the 195 model of the system in 1969. In 1970, the IBM-360 architecture was replaced by the IBM-370 architecture. The inner architecture of the IBM-370 processors clearly show the details of modern superscalar microprocessors. So, the IBM-360/370 architecture became the most popular architecture in 60-, and 70-ies.

The IBM-360 computer contained several cabinets and was installed in a separate room. The central processing unit (CPU) was housed in the main frame of the main cabinet of the computer. Therefore, a large computer was usually called (and still is called) as a mainframe. In our country, counterparts

computers with this architecture were known as the EC-1010,..., EC-1065 models. The next generations of large IBM computers were designed on the microprocessors, which instruction sets had inherited the IBM-360/370 instructions to meet the portability requirements of the software.

The computer history shows that successful architectures are not those architectures that incorporate advanced scientific ideas, but those that are supported by the best sales management and market conditions. For example, the company Burroughs had introduced in their computers many technical innovations, but they did not contribute to its success. So, in its computer B5000, the multiprogram operating system, and the virtual memory were used at the first time, which preceded their widespread adoption in the decade. But the computer performance in 1963 did not satisfy the users. In the most perfect machine of this brand B6500, sample 1966, the operating system provided the multiprogramming, parallel processing, time-sharing operation, and even the implementation of programs with different instruction sets. But these achievements did not save the company from the downfall.

Another example is a company Control Data Corporation (CDC). Seymour Cray, its founder, in 1963, has developed the CDC-6600 model consisting of multiple ALUs, and peripheral processors. He has found many signs, which were introduced later in the RISC-processors, such as, simple instructions; instructions working with the registers are separated from other instructions; register instructions have three address fields; instruction format is simple and has the equal field widths; pipelined instruction implementation; multiple hardware resources are redistributed between the instruction streams, as in the modern superscalar processors; register renaming technique.

As a result, the speed of the CDC computer was three times the speed of the Stretch computer, but it has not received the popularity. Ideas, tested in

it, have been introduced in the first Cray supercomputer Cray1, which entered service in 1976.

In 1965, the company DEC pushed the 12-bit PDP-8 computer, which gave the impetus for the development of minicomputers. It was the first computer, which was sold for less than 20 thousand USD. The presentation of the DEC PDP-11 architecture in 1970 was the most significant. A minicomputer architecture is characterized in that, that all of its processors and peripherals are connected by the asynchronous bidirectional common bus. This allows the computer to form a configuration in a modular fashion.

A few years later this architecture was repeated in the USSR in the CM-4, M-4030, Capaтов computers, and later — in microcomputers Электроника-60, and ДВК.

The PDP-11 architecture was perfect one, so it has become very popular among the programmers. This architecture is repeated in minicomputers, and workstations of the VAX architecture after its upgrade. On the VAX architecture, and its successor Alpha-RISC the DEC company has broken its story because it could not compete with Intel architectures in the market, in 90-ies.

In 1968, the Nova architecture of the Data General company also was included in the minicomputer history. This model was most popular in the world among the minicomputers for its price of only eight thousand US dollars. This architecture is distinguished by the built-in read-only memory (ROM), which stored the software. Then this architectural feature was integrated in all microcomputers.

In the late 60-ies, in Kiev Institute of Cybernetics the minicomputer MUP-1 has been developed and implemented in the production. It is distinguished by the fact that his high-level language interpreter was implemented in the form of the microprogram firmware. This computer was

respected among engineers, researchers, thanks to user-friendly interface. His successor MИP-2 had a console with display and stylus, and was considered as an engineer personal computer (PC).

The quick growth of the calculator market in the late 60-ies was the direct cause of the microprocessor invention. It is believed that the appearance in 1971 of the I4004 chip, developed by the Intel engineers, was the beginning of a microprocessor era. The chief designer of this microprocessor, M. E. Hoff has created it after he has been inspired by the PDP-8 architecture. The emergence of the microprocessors became possible, clear and inevitable when the number of transistors on a chip became more than a few thousand.

The architectural features of the microprocessors were constantly expanded with increasing the number of transistors on a chip. Back in the mid-1960s, Gordon Moore, one of Intel's founders, analyzing different successful chip manufacturers, noticed that about every two years the number of transistors doubles in the chips. This law, named after the Moore, have adopted by the Intel economists and they demanded that the designers of new chips perform it, because it was the key to business success in the field of microelectronics. As a result, this law is strictly carried out for decades and is still in use.

Therefore, the microprocessor architectures were constantly growing with the grow of the number of transistors in a chip. Thus, the I8080 microprocessor had ca. 4500 transistors and provided a single program execution. The I8086 microprocessor with 29 thousand transistors had several programs running under the operating system. 275 thousand of transistors in the I80386 microprocessor provided already the multitasking and the virtual memory.

According to the Moore's law, the memory chips also have developed. The advent of the cheap dynamic memory chips in the early 1980s allowed to design small-sized memory with the capacity of up to 1 MB, and thus ensured the mass production of personal computers. After the RAM capacity reached the values 4-10 MB, it has become possible to run the operating system with a graphical interface, such as Windows-3. When this capacity reached approximately 100 MB, it was possible to process the multimedia data in computers.

New architectural features in the microprocessors repeated the same features in the mainframes of the 1960s - 1980s, while the number of transistors on a chip did not become greater than the total number of transistors it the mainframe chips. This limit is equal to about 1 mln. transistors and has been crossed in the early 90-ies.

At present, several billion of transistors are available for developers of new microprocessors. All the architectural ideas, which were embedded in the old computers, have been exhausted. Moreover, miniaturization is approaching the limit of using the silicon technology. For the constant growth of the computer speed the new architectural ideas are of demand.

Based on the review of the computer and its architecture history we can formulate the following conclusions.

• The advent of computers with the same architecture occurred due to the high programmer labor intensity and the need for software portability between different computers.

• Modern architectures, to a large extent are formed as a set of reinterpreted architectural features which were invented before.

• Most of the architectural features were invented at a time when the hardware resources were severely limited.

• The purpose of the computer architecture, like military tasks, scientific calculations, economic calculations, management, affects it.

• The development of computers and, consequently, their architecture is greatly influenced by the commercial benefits and militaristic needs.

• Miniaturization and new inventions allowed to increase the memory amount. When a certain memory limit of the computer was achieved then the architecture, programming techniques, and operating system were fundamentally changed.

• Not only the potential effectiveness, speed, size, etc. of a new architecture, but the commercial management, competition, and market conditions affect the computer architecture success.

• The high cost of hardware and time resources, a small amount of RAM of computers in the early 60-s led to introduce a system of time-sharing, multi-tasking, memory protection, virtual memory, cache memory, remote access to the processor.

• The architecture represents the main knowledge about the computer potential properties, which serve as a standard both for computer designer and for programmers.

#### **1.1.2 Basic definitions concerning the architectures**

To understand the structure of the existing computers, or successfully complete the development of new computers, to communicate with experts and to understand the relevant technical literature, it is necessary to know the number of definitions, axioms and principles of computer science. Some of them are listed below.

*State of the computer* is a state  $St_i$  of all its memory cells in discrete time moment *i* of its operation. For example, the microprocessor state is determined by the content of its instruction, data registers, program counter,

flag triggers, interface buffers, as well as all the RAM cells. When we deal with the hand made model on the sheet of paper, then its empty squares can serve as the memory cells, in which the writing is performed by a pen.

The different *constructive objects* can be stored in the memory cells. They represent individual bits, characters, words, strings, numbers, as well as more complex objects, such as records, lists, files, arrays, and the like. These constructive objects specify the state of the computer according to the semantic of the computational process implemented in.

*The computational process* is a succession of states  $St_i$  of a computer, beginning by the initial state  $St_0$ , and ending by the resulting state  $St_E$ . Moreover, the resulting state can be inaccessible, for example, in a digital signal processor, or in the control processor. In the initial state, the defined memory cells store the initial data, and in the final state the cells store the calculation results. During the computing process, the constructive objects are read from the memory, converted, calculated, forwarded, and stored by means of certain operations, instructions, which are specific to the computer.

**The algorithm** is the computational process of calculating a specific function *F* in the computational model, which is described by the strict mathematical concepts.

This definition was firstly formulated by E. L. Post, and A.Turing. In the Turing's definition, the Turing machine is taken. This machine is constructed as the endless tape and the control unit. The writing-reading head can read and write data bits on the tape. The control unit controls the movement, and operation of the head according to the algorithm. The state of this model is determined by the state of the control unit, the position of the head, and the state of the tape, and is called the Turing machine configuration.

The concept of the algorithm exists as an intuitive concept, rather than as a strictly limited definition. This concept implies firstly, that there must be a specific subject or a processor that is able to read, recognize these objects and correctly perform operations with them according to the algorithm.

Second, certainly the algorithm is designed to efficiently compute some useful function *F* in order to obtain the correct result for a particular kind of input data. Moreover, the reaching of that result must be guaranteed.

Third, for ease of understanding and implementation of the algorithm, the minor details of the computational process (which usually do not affect the computational model) are not taken into account. A set of different computational models is usually used in a practice. They are distinguished both in the field of application and in the abstraction level. In both situations, the model must be as simple as possible to arrange the computational process in useful manner.

The concept of the constructive objects serves not to consider the minor details of the algorithm as well. The constructive objects usually form a set of abstraction levels. For example, if we consider the array processing then we may not consider the separate data of that arrays, and moreover, we could not take into account the processing of separate bits of that data.

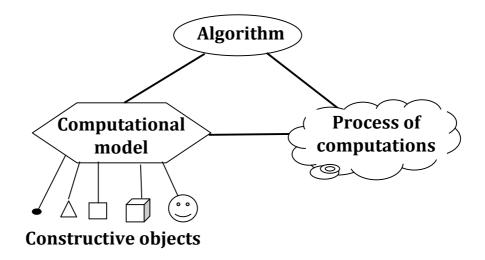

So, the algorithm concept is inseparably connected with the meanings of the computational process and computational model, which deal with the constructive objects (see Fig. 1.1). When we say about some computational process, then we consider that it takes place in a given computational model. When we have the proper computational model, then we may arrange some computational process on it. And in both these situations, we deal with the algorithm, which meaning remains not exact.

Therefore, the definition above is merely an explanation of the algorithm with the goal to represent the architecture concept below. Thus, the algorithm can exist apart from the computational model - a model of the rules list — or be part of the model as a control unit in a Turing machine, or to be

the very model, for example, a finite state machine model or the dataflow graph model. For example, if the executor of the algorithm is a man or a programmed processor, then the algorithm is traditionally referred to us as a list of instructions that should be followed consistently.

Fig.1.1. Algorithm concept

So, we can give the following definition of the architecture and other definitions connected with.

*The architecture* is a model of a real computer with a level of details, which is sufficient for its development or programming, and provides the implementation of the corresponding set of algorithms.

**The program** is an algorithm that is specified on the computer architecture by the means of the algorithmic language or the machine codes depending on the level of the architecture details, or the abstraction level. So, a program, which is written for a particular architecture, should be computed for the same input data with the same intermediate and final results on different computers that have the same architecture.

*The architecture from the developer's point of view* is a computer model with a level of details that is sufficient for its development and

production. The architecture, as a rule, includes information about the instruction set, address space, address management, system interrupts, memory protection, interfaces, peripherals, that is, all information on the detailed terms of reference for the computer development. Description of this architecture does not include information on the element basis, its speed, computer dimensions, power consumption, security settings, etc., as they do not directly influence the computing process.

*The architecture from the programmer's point of view* is a computer model with a level of detail which is sufficient for a successful programming certain computational tasks at a particular algorithmic language.

For example, a programmer in Pascal language takes into account the model of computer memory that is addressed by a 32-bit bus, with the ALU, which handles integers or floating point numbers, with the memory at an arbitrary amount of magnetic hard disk, a keyboard and a display, the access to which is provided by the procedures that he/she can find in the library of Pascal procedures.

Each line of the algorithm, described in the assembly language, means a specific machine instruction, performing basic operations with data or controlling the selection of the next instruction. Therefore, the assembly language programmer needs to know the computer architecture perfectly in details up to the separate register and its bit, the interrupt code, the peripheral device address, and the like.

Some of the architectures for the high-level language is defined as an *interface* between the language and the system software, which directly implements the compiled program. The operating system or the virtual machine model usually serves as such an interface.

*The architectural platform* is a common computer architecture, which guarantee to be consistent over the next few years. The architectural

platform can be used in the new computing tools and computers, ensuring the software compatibility, the use of prefabricated components in computers, connection of existing peripherals and devices manufactured by other companies. The most famous architectural platform is i80x86. Its synonym is 32-bit Intel Architecture (IA-32).

*The architectural paradigm* is a set of common principles and approaches for designing computer architectures. For example, the computer ENIAC, was made using the special processor paradigm, which uses the mapping the algorithm graph into the processor structure with configurable connections. That is, the graph node is associated with an operating unit, i.e. adder or multiplier, and its edge is mapped into the link between the operating units. Most of the computers mentioned above are built on the von Neumann machine paradigm, which will be discussed below.

#### **1.1.3 Principles of computer design**

To explain the choice of a particular computer architecture and instruction set, let us consider the principles of their design, which were invented and perfected over the years of the computer history.

**The hierarchy principle** means that the complex computing function  $F = (F_1, F_2, ..., F_i, ...)$ , that is the composition of functions  $F_i$ , is implemented in the calculator  $S = (S_1, S_2, ..., S_i, ...)$ , where each function  $F_i$  is performed by the certain unit  $S_i$ . In turn, functions  $F_i$  are performed by modules of the system at a lower level of the hierarchy.

The principle of hierarchy allows us to understand, design and implement complex technical systems, which are computers. The overview, synthesis (design), or analysis of the system is usually directed upwards (*down-up concept*), i.e. from the elements to complex units or downward

(*up-down concept*), when the system is first treated at a high level and gradually descends to the level of elements.

This principle is the basis of the design of any complex technical system. To deal with some complex object it must be represented as simple as possible. According to this principle, we can see the different abstraction layers in hardware, data structures, and software. So the computer is built as a set of building blocks, which in turn are implemented on the base of modules, such as ALU, register, counter, and the like. Those, in turn, are performed on the basis of certain logical elements. Similarly, the hierarchical dataset consists of individual words, which, respectively, are sets of bits. The complex program consists of several software modules, which contain routines that are written as a sequence of operators, and in the compiled program each statement is substituted by one or more machine instructions.

*The concept of operational and control automata* claims that the processor *S* can be effectively realized, developed and implemented as the composition of operational and control automata. The first one performs a specific set of operations with the data, and the second one controls the execution of these operations according to a given algorithm. For example, a data processing unit, which is discussed below, is composed of an arithmetic logic unit (ALU), data registers, representing an operating automaton, and the control automaton, which supplies control signals to the registers and ALU according to algorithms of the processor instruction performing.

According to the *principle of program control*, the operations of the function *F* calculation are coded by instructions that are decoded by the control automaton and executed in the operation automaton. The process of calculating the function *F* is described by the algorithm that is represented as a list of instructions, in which their order is encoded as well. I.e., such a list

represents a program. To change the order of instructions dynamically the control, or branch instructions are used.

*Microprogram control principle*. It is derived from the previous principle. According to it, the implementation of the complex operation, such as a processor instruction, is decomposed into micro-operations, which are carried out in the serial-parallel order by separate units of the operational automaton. Micro-operations, which are performed simultaneously, are encoded in a single microinstruction, in which also the order of microinstruction execution is encoded. A set of microinstructions is named as a *firmware*, and is stored in the read-only memory (ROM).

The principle of storing programs and data in a single memory (von Neumann principle) is the program control principle, according to which the instructions are stored in memory and processed in the same way as the data are, the next instruction starts only after the end of the previous instruction, the sequence of instructions is given by the natural order of their location in memory except for the branch instructions. Since the memory usually has a linear addressing, sequential instructions are fetched from it by an instruction counter.

Thanks to this principle, it is relatively easy to define the computational process in computers and carry them to build programs. In our time, the computing process can be arranged by many other methods using the automating programming, designing architectures, which are working on different principles. But this principle remains the most common principle of both programming and designing of most architectures.

But the von Neuman machines have a lot of disadvantages, which limit their use in our time. In the computer, which is running on this principle, the instructions and data types are distinguished implicitly. It is believed that the word, which is fetched to the instruction register, is an instruction but not a

datum, an arithmetic instruction refers correctly to the data of some particular type, and the branch instruction takes a branch to a specific instruction of the program. But it is possible that the arithmetic instruction would fetch the data of improper type, or even not the data at all. When the branch instruction occasionally makes the jump to the data array, the computational process is failed. Such situations occur in most cases of malfunctioning of the computers.

It is also contrary to the requirements of programming languages, according to which the operations refer to the constructive objects (numbers, strings, arrays) explicitly, and the mismatch of operation types and objects is not allowed.

According to this principle, it is impossible to perform simultaneously multiple instructions in the processor. Therefore, due to the strict observance of this principle, it could not increase the computer performance by the parallel implementation of operations, which hampers the development of computer technology. In modern architecture, this principle is violated in hardware to improve performance. Because of this, the reliability of the software, which has developed in accordance with the von Neumann principle, can decline.

*The synchronous control principle* means that all the computer memory elements, including registers, change their state *St<sub>i</sub>* simultaneously under the influence of a common clock impulse generator, and time is measured at discrete moments. Then the period of clock impulses is determined by the maximum delay of the signal which is propagated from one clocked register to other one.

Every computer, which was designed in the past three decades, can be considered as a set of logical circuits and a set of registers that are clocked by a common clock signal. The process of information processing consists in that

signals, outputted from the registers at the beginning of each cycle, are propagated through logic circuits with inherent delay and converted therein according to logical functions, and are stored in the registers at the end of the clock cycle. This information processing order in the physical layer of design is clear and is supported by all modern computer-aided design (**CAD**) tools for the digital circuits.

At a higher level — the level of parallel processes — due to this principle, the parallel computing processes terminate or exchange the results simultaneously under a single source of control instructions, which is the manager of the operating system. The synchronous control principle manifests itself at the level of procedures as well. For example, the consistent implementation of program streams is planned by quanta of time, or in the case of the multiprocessor system programming.

*An asynchronous control principle* sometimes is used, when the memory element changes its state only by the special signal of the data availability. This signal is generated by a logic circuitry which processes the data. Therefore, the computer state can be changed faster, and the computer can have higher performance. But it is more difficult to design such a computer, and its speed can be lost when it is connected to the devices controlled synchronously or performing algorithms with the feedback of data. This principle is often used in telecommunication systems, for example, in the computer network protocols.

Due to *the principle of balanced flexibility and specialization*, the optimal computer architecture lays on the boundary of universal and specialized architectures. It is known from the computer design practice, that the general purpose processor is capable performing a large set of algorithms, but its speed, power consumption, size, and cost are two — three orders of magnitude worse than these parameters in the application specific computer

configured to perform a single algorithm. The mainframe computers, which are designed to perform a certain set of sophisticated algorithms for a small period of time, i.e., supercomputers have the largest parameters of price, performance, size, power consumption.

In addition, a plurality of computer algorithms for a new architecture is defined by the number of programs that can be created for it. This number is limited as well as the program design time, or the number of the programmers in the development team is limited.

Therefore, designers of new computational tools are always looking for a compromise between the flexibility and cost of a new computer in its production and use, including the software, trying to use the old, wellbehaved architectures. For example, mobile communication devices perform more and more algorithms, but this set of algorithms is limited to, at least, opportunities of these devices to save the energy, their battery charge, and weight. This also corresponds to the following principle.

According to *the principle of effective multi-functionality*, increasing the functionality of the computer should not lead to a proportional increase in its cost and complexity. In this regard, the von Neumann architecture is perfect, as it ensures the execution of arbitrary algorithm with unchanged hardware costs.

*The principle of parallel processing of information*. Due to this principle, the independent steps of calculating a function *F* and management are shared between several operating and control automata (or processors), in order to achieve the high performance and (or) high reliability of computers.

The most apparent and therefore, more common are the sequential algorithms which are described, for example, by sequential programs. Operators of such an algorithm are executed sequentially on a single resource,

such as an ALU in the Neumann processor. But to accelerate the algorithm, using the same element basic, it is possible only having involved the principle of parallel processing.

According to *the principle of pipelined computing*, the calculation of the function F is divided into successive stages  $F_1$ ,  $F_2$ , ...,  $F_K$ , each of which is calculated in a separate computing resource  $S_i$  of the pipelined processor. The operand  $X_j$  is sequentially processed while passing through resources  $S_i$ , called *pipeline stages*. Due to the fact, that the flow of the data  $X_j$  through the pipeline is a continuous one, the overall throughput is increased up to K times, and up to K operands are considered to be processed in parallel.

*The variability principle* means the ability to change a set of computer components and connections between them. This principle is manifested in the properties of persistency and scalability of computers, the possibility of adapting the architecture to the specific nature of the task. It ensures the implementation of the multifunctionality principle.

The homogeneity principle is that the structure of the computer or parts of it includes the same elements and the repetitive connections. This reduces the cost to design, manufacture and operation of the computer. The computer memory, consisting of thousands or millions of identical cells, is based on this principle. All multi-processor computers consist of multiple identical processing elements. Moreover, due to the principle of homogeneity, the task scheduling in the multiprocessors is significantly easier than in the heterogeneous computers, consisting of unequal processors.

*The principle of unification* is a universal principle of creation of technical systems. This principle insists that an object that must interact with other objects, has to be created according to the standard requirements. The object is connected seamlessly unified with other objects even when they were manufactured in different locations and at any time. The idea of a

computer architecture is the result of this principle so that every program runs correctly on any computer of the same architecture.

The main factor in the unification of the computer technology is the interface. *An interface* as a standard means of connection in a computer is used both in busses and in programs. The interface between a man and hardware and software system is of particular importance because it helps to effectively create synergies between the various operators and the computer using the same software.

#### **1.1.4 Architecture hierarchy**

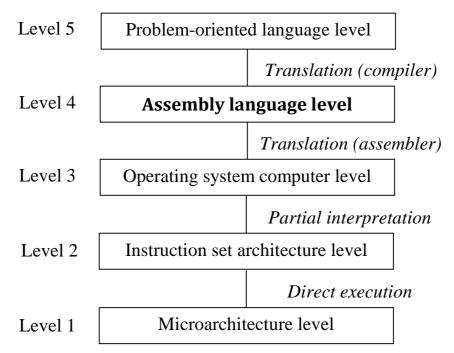

Due to the principle of the hierarchy, two or more architecture levels are considered in the modern computers. The computers with as many as five levels exist, as shown in Fig. 1.2.

Fig.1.2. Hierarchy levels of the architecture

The *microarchitecture level* is considered as the bottom architecture level 1. It describes the details of the hardware architecture implementation. They are how the arithmetic and logic instructions are implemented in ALU, the inner structure of the registered RAM, how the busses connect the units of the processor, and which control signals control the data writing into registers and data output to the common buses, and so on.

Each processor series has its own microarchitecture. Therefore, the microarchitecture can be valued as a kind of the architecture rather relatively, because it depends on the hardware element basis.

On some processors, the operation in the microarchitecture is controlled directly by hardware. On other processors, it is controlled by a microprogram. So, the *microprogram* is an interpreter for the processor instructions at the level 2 architecture. It fetches, examines, and executes instructions one by one, using ALU and registered RAM to do so. For example, for an ADD instruction, the instruction would be fetched, its operands located and brought into registers, the sum computed by the ALU, and finally the result routed back to the place it belongs. On a processor with hardwired control, similar steps would take place, but without an explicit stored microprogram to control the interpretation of the level 2 instructions.

The level 2 architecture is called as the *Instruction Set Architecture* level (**ISA** level). Every computer manufacturer publishes a manual for each of the computers it sells, entitled "Machine Language Reference Manual," or something similar. These manuals are really about the ISA level, not the underlying levels. Moreover, the level 1 is usually a secret information. When such a manual describes the processor's instruction set, it is in fact describing the instructions carried out interpretively by the microprogram or hardware execution circuits.

The next level is usually a hybrid level. Most of the instructions in its language belong also to the ISA level. In addition, there is a set of new instructions, a different memory organization including the memory protection, the ability to run two or more programs concurrently, and various other features.

The new facilities added at level 3 are carried out by an interpreter running at level 2, which, historically, has been called an operating system. *The Operating System* (OS) is a set of programs that allows the user to organize effectively the performing a variety of computing tasks in the computer, and take the computer system in working condition. The main tasks of OS, running at level 3, are loading the user program and data in the memory, starting its operation, providing the parallel implementation of several programs in the time-division mode, triggering and working off the exceptions. The special instructions and hardware, which are not accessible directly from the user programs, support these tasks.

Those level 3 instructions that are identical to level 2's are executed directly by the microprogram (or hardwired control), not by the operating system. In other words, some of the level 3 instructions are interpreted by the operating system and some are interpreted directly by the microprogram (or hardwired control). This is what we mean the level 3 by the "hybrid" level.

There is a fundamental break between levels 3 and 4. The lowest three levels are not designed for use by the usual programmer. Instead, they are intended primarily for running the interpreters and translators needed to support the higher levels. These interpreters and translators are written by people called the system programmers who specialize in designing and implementing new virtual machines. Levels 4 and above are intended for the application programmer with a problem to solve.

Another change occurring at level 4 is the method, by which the higher levels are supported. Levels 2 and 3 are always interpreted. Levels 4, 5, and above are usually supported by translation. Yet another difference between levels 1, 2, and 3, on the one hand, and levels 4, 5, and higher, on the other, is the nature of the language provided. The machine languages of levels 1, 2, and 3 are numeric codes. Starting at level 4, the languages contain words and abbreviations meaningful to people.

Level 4, the *assembly language level*, is really a symbolic form for one of the underlying languages. This level provides a method for programmers to write programs for levels 2, and 3 in a form that is not as unpleasant as the virtual machine languages themselves. Programs in assembly language are first translated to level 2, or 3 language and then interpreted by the appropriate virtual or actual machine. The program that performs the translation is called an *assembler*.

The architecture level 5 usually consists of languages designed to be used by applications programmers with problems to solve. Such languages are often called *high-level languages*. A few of the better-known ones are C, C++, C#, Java, Pascal, Python, and PHP. Programs written in these languages are generally translated to level 3 or level 4 by translators known as compilers.

In summary, the key thing to remember is that computers are designed as a series of levels, each one built on its predecessors. Each level represents a distinct abstraction, with different objects and operations present. By designing and analyzing computers in this fashion, we are temporarily able to suppress irrelevant detail and thus reduce a complex subject to something easier to understand.

The set of data types, operations, and features of each level is called its architecture. The architecture deals with those aspects that are visible to the user of that level of abstraction. Features that the programmer sees, such as

how much memory is available, are part of the architecture. Implementation aspects, such as what kind of technology is used to implement the memory, are not part of the architecture. Therefore, the levels 1, 2, 3 we can mean as the architectures from the designer's point of view, and the levels 4, 5 - as the architecture from the programmer's point of view. In common practice, however, computer architecture and computer organization mean essentially the same thing.

#### **1.1.5 Problems**

1) For which purpose the OS, and the multiprogramming mode invented were?

2) Why the IBM company rent their computers but not sold them in 50-s?

3) Estimate the dimensions, speed, and power consumption of a hypotetic mainframe in early 60-s, which implements the architecture of the Pentium microprocessor, containing 3.1 mln. transistors, and operating with the clock frequency of 60 MHz. Note, that in 60-s the main computer module was the printed circuit board of dimensions ca. 150x200x15 containing ca. 40 transistors, operating at 1 MHz with the switching current approx. 10 mA, power voltage 12 V.

4) Estimate the volume of the tape storage shelves for 1 GB of data in the mainframe data centre. Note, that the tape of the width 16 mm, and thickness of 20  $\mu$ m stores 30 bytes per mm.

5) RAM on the ferrite cores has the volume of 1 MB. A worker in 60-s can weave 50 cores per minute making the storage, and had a fee 300 USD per month. Estimate the cost of the RAM.

6) Each line of the Basic program has its own number. The Basic interpreter was the first product of the Microsoft company. Explain, why.

7) The algorithm is given by a formula  $y = a \cdot x^2 + b \cdot x + c$ . Explain, what are the constructive objects, computational model, and computational process.

8) The algorithm of the finite state machine is given by the state graph. Explain, what are the constructive objects, computational model, and computational process.

9) The algorithm of the finite state machine is given by the network of this machine. Explain, what are the constructive objects, computational model, and computational process.

10) The algorithm of calculating the sum values is given by the Excel table. Explain, what are the constructive objects, computational model, and computational process.

11) The algorithm is given by the program on the assembly language. Explain, what are the constructive objects, computational model, and computational process.

12) The algorithm is given as the text on the HTML language. Explain, what are the constructive objects, computational model, and computational process.

13) Write the algorithm of the multiplication of two digit decimal numbers by the school method. Explain, what are the constructive objects, computational model, and computational process.

14) Describe the architecture of the decimal handheld calculator from the programmer's point of view.

15) Describe the architecture things of the processor implementing the HTML language (constructive objects, structure, programming language, etc.).

16) Write the program for computation (a sequence of the pushed buttons) of the 4-th order polynomial for the architecture of the handheld calculator (modeled by the Calc program).

17) Name 6 most popular architectural platforms.

18) Draw the graph of the algorithm calculating the function  $z = a \cdot x^2 + b \cdot x + c + d \cdot y^2 + e \cdot y + f \cdot x \cdot y$ . How many steps has to perform the von Neuman machine, and the computer, which calculates this function fully parallel? Calculate the speed-up factor.

19) Draw the pipeline structure, which calculates the formula in the task 7. Calculate the speed-up factor comparing to the sequential machine, and considering that the data flow through the pipeline is unlimited.

20) Propose the instruction set of the architecture, which performs the task 18.

#### 1.2 Element basis of computers

As shown above, the computer architecture has evolved interrelated to the development of their components. The revolutionary impetus to the informatics and computerization of the society have been the emergence and widespread of the technology of the development and manufacturing of large scale integral circuits (ICs). Although, the computer architecture, in principle, has no information on the element base, it is largely determined by the characteristics of ICs, which it uses. Therefore, hereinafter we do a brief look at element basis of modern computers.

#### **1.2.1 Element basis of integrated circuits**

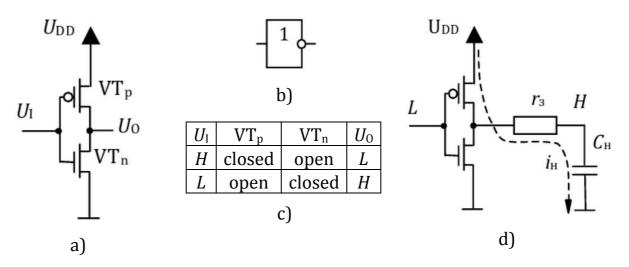

ICs are both the most important products of the electronic industry and the basis for all items of computer equipment. The transistor is an elementary component of the IC. The inverter, the simplest element of IC, consists of two *complementary* transistors with the structure of the *metaloxide-semiconductor* (CMOS) as shown in the functional diagram in Fig. 1.3.

Fig.1.3. Functional diagram of the invertor (a), its symbol (b), its truth table (c), invertor connected to the loading (d)

The p-channel transistor VTp in the inverter is always in the opposite state, that is in the complementary state with respect to the n-channel transistor VTn, as shown in the truth table in Fig.1.3, c. In this table, the symbol H (high) is a high signal level, i.e. logic 1, a L (low) is a low level, or logic 0. The CMOS inverter has three components of power consumption: static, dynamic consumption and consumption in the load.

In the static mode, either the top or the bottom transistor of the inverter is closed. Therefore, the CMOS inverter in this mode consumes almost nothing. At the time of the inverter switching, both transistors in a very short period of time can become open and then there is little impetus to the dynamic current consumption.

But most of all the inverter power dissipation is due to the load current, which charges or discharges the load capacitance  $C_{\rm H}$  and flows through the resistance  $r_{\rm w}$  of the connection and resistance of the open transistor. The energy  $E_{\rm s}$ , which is considered to be consumed by the inverter when it is switched, is equal to the energy dissipated in the resistor  $r_{\rm w}$  and open transistor, and is the charging energy of the capacitance  $C_{\rm H}$ , that is, it can be estimated as

$$E_{\rm s} = \frac{C_{\rm H} U^2_{\rm DD}}{2},$$

(1.1)

where  $U_{DD}$  is the supply voltage, which is approximately equal to the difference of the levels L and H,  $C_{\rm H}$  is the equivalent load capacity, which is equal to the total capacity of the CMOS transistor gates in all circuits, which are connected to the inverter output, plus the communication line capacity.

As the number of switchings per second of the inverter circuits and similar ICs is proportional to the clock frequency  $f_c$ , the power consumption of the computer is also proportional to this frequency. Also, according to (1.1), this consumption is proportional to capacitance, which depends not only on the complexity of the circuit but also on the technology of its manufacturing. The value  $C_H$  is inversely proportional to the *design norm* of IC, which is equal to the minimum width of the constructive elements of IC, for example, the width of the wire, or the transistor gate. Furthermore, the decrease of  $C_H$  is proportional to its charge shortening and hence, to the inverter speed and in general, to the IP clock frequency. Therefore, with each new generation of IP technology the energy, produced by the chips, is significantly reduced and their performance is increased.

According to the formula (1.1), it is worth to reduce the power voltage  $U_{DD}$  to effectively minimize the power consumption. But when it is decreasing below the limit of 0.9 V, then one of the CMOS transistors of the inverter is not enough closed and proceeds substantial constant current.

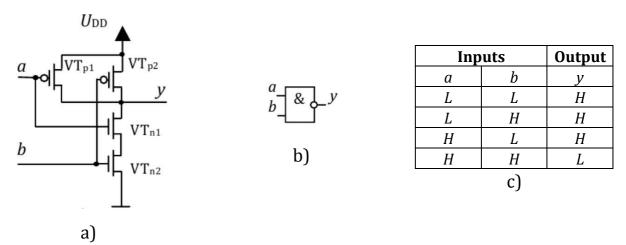

A two input logic element (LE), called the *logical gate* is formed of four transistors as in Figure 1.4. If both inputs a and b are set high, the transistors  $VT_{n1}$  and  $VT_{n2}$  are opened, so that the output is set at a low level, while the transistors  $VT_{p1}$  and  $VT_{p2}$  are closed. In another combination of the input

signals, at least one of transistors  $VT_{p1}$ ,  $VT_{p2}$  is opened and one of  $VT_{n1}$ ,  $VT_{n2}$  is closed, and the output is a high signal level.

Fig.1.4. Functional network of the AND-NOT gate (a), its its symbol (b), its truth table (c)

The basic element of computer memory is a flip-flop, which stores a single bit of information. There are triggers such as latch and synchronous trigger. The *latch* is a trigger, which has two main modes: transparent mode, in which the trigger output repeats the information at its input, and storing mode when it stores a bit in the internal bistable circuit with the state Q = 0, or Q = 1. The latch mode is changed by the level of the input data or clock signal. Since this trigger has the transparent mode, in which the output signal is changed regardless the clock signal, it is often called as the *asynchronous trigger*.

*The clock signal* is a control signal, which periodically goes from 0 to 1 and then back to 0. The clock signal is usually referred to as C or CLK or CLOCK. Using the clock signal to control the operation of the trigger allows the developer to set a predetermined moment of time, at which data can be stored in the triggers of the device.

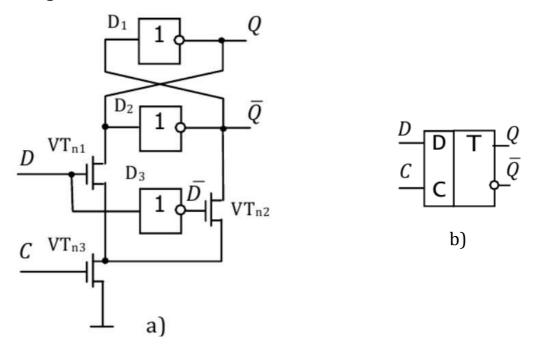

Synchronized D-latch in the IC is created by the network as in Figure 1.5. Its inverters D1 and D2 form a bistable circuit via the feedback. If the

clock signal C = 1 opens the transistor  $VT_{n3}$ , the input signal D or opens either transistor  $VT_{n1}$  or transistor  $VT_{n2}$  so that the bistable circuit goes to a state corresponding to the signal D. In this case, a trigger goes to the transparency mode, and arbitrary changes in the signal D are transmitted to the output. After closing the transistor  $VT_{n3}$  when C = 0, the trigger goes into the storage mode and the bit, stored at the last moment, when C = 1, is outputted unchanged.

Fig.1.5. Functional network of the D-latch (a), its symbol (b)

The networks, where the latches are used, may have unpredictable behavior. So, the signal D can be distributed through a chain of seriesconnected latches, when they are in the transparent mode, or in the network the oscillations can be excited when the latches are connected through the feedback. Therefore, to prevent such phenomena, typically only synchronous triggers are used in all modern computers.

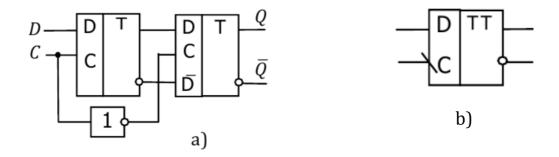

In the simplest network of the synchronous trigger, or *flip-flop*, two simultaneous synchronized latches are connected in series, as shown in Figure 1.6.

Fig.1.6. Functional network of the synchronous D-flip-flop (a), and its symbol (b)

The first latch acts as a master stage and is responsible for receiving the data. The second latch is a driven stage and is intended for the storage of the data, received from the master stage. In order not to propagate the data simultaneously through two stages in the transparency mode, the first and the second latch are synchronized by the opposite phases of the clock signal C. Consequently, the data from the master latch is rewritten to the slave latch (and becomes visible at the output Q) when the clock signal goes from C = 1 to C = 0. Because of such properties, this network is considered to be sensitive to the rising clock edge.

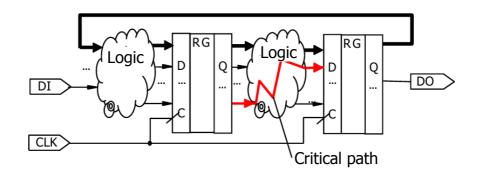

Any computer network can be represented as a set of combinational networks and a set of registers, built from synchronous triggers. These sets are linked by the respective communication system, such as in the Figure 1.7.

With the single-cycle synchronization, all the computer registers are implemented as synchronous ones and are clocked by a single clock signal. The clock signal transmission network in the modern chips from its source to all triggers is designed with the utmost care. Due to this, it provides minimal delay skew of the clock edge arrival to each trigger. Therefore, the minimum period  $T_{\text{Cmin}}$  of the clock signal of a chip is estimated as the maximum delay between the output of an arbitrary flip-flop and the input of another one. That is, the signal between these triggers passes through the critical path in the combinational network (Figure 1.7). Accordingly, the maximum clock frequency of the processor, to a certain extent, determines the computer speed and is defined as  $f_{\text{Cmax}} = 1 / T_{\text{Cmin}}$ .

Fig.1.7. Functional network of the arbitrary computer

With the constant decrease of the design rules, the IC technology has moved into a period when the gate delay becomes less than the delay in the connections between gates. In addition, the interconnect wire thinning and the corresponded increase of their resistance, as well as the increasing of the frequency  $f_{\text{Cmax}}$  of up to several gigahertz, lead to substantial signal fading in interconnects, as well as a reduction of the propagation velocity (Fig. 1.3, d). This has led to the fact that on the one hand, to maintain the desired shape of the logic signals it is necessary to insert additional buffers and triggers, on the other hand, the growth of the clock frequency  $f_{\text{Cmax}}$  stopped at the limit values of 5 - 7 GHz.

### 1.2.2 Integral circuit classification

The complexity of digital ICs is generally expressed in the number of equivalent two-input logic gates. According to this number all ICs are divided into Ics of the small scale of integration, *Large-Scale Integration* (LSI) and

*Very Large-Scale Integration* (VLSI). VLSI circuit consist of more than hundred thousands of gates.

VLSI circuits are divided into microprocessors, microcontrollers, memory ICs, **ASIC**s (*Application Specific Integral Circuits*), and **ASSP**s (*Application Specific Standard Products*). Modern VLSI circuit can contain more than ten million gates. In addition, the memory chips have a volume of up to billions of bits, wherein to store a single bit, one to ten transistors are needed.

*The microprocessor* is the main operating unit of the computer. Its functionality is not defined, not only during their development, production but also during its use. It depends on the user programs and OS (see. Table 1.1).

*The microcontroller,* as the instruction controlled processor, has the same properties as the microprocessor. But its functionality is usually constant and determines the functionality of the product in which it is embedded. This means that the device performs a single program, which usually remains unchanged throughout the time of use of the product.

*The Digital Signal Processor* (DSP) belongs to a separate subset of microcontrollers. Its architecture is adapted to the signal processing problems.

The **ASIC** chip has this name because of its functionality, which is put into it during the design and production. Therefore, ASIC implements a one, but a complex function. Examples of ASIC, or custom VLSI are the modem circuit, the drive controller, Ics of the computer chipset, encryption IC. Since the cost of VLSI design is constantly increasing, their development and production can be profitable when the production of the series reaches millions of chips.

The chip of **ASSP** can have the synonym of the multifunctional VLSI. The functionality of ASSP is less than the functionality of a microcontroller, but it is enough to set it up in a variety of different applications. From the perspective of the designer, the ASSP is the multi-purpose ASIC, which has the ability to be adapted to the application. Examples of ASSP are IC of dedicated memory, the microcontroller with a specific set of peripherals, such as the MP3-player, the decoder of the MPEG image.

| IC type         | Design stage | Manufacturing | Introducing and |

|-----------------|--------------|---------------|-----------------|

|                 |              | stage         | use stage       |

| ASIC            | known        | known         | known           |

| ASSP            | unknown      | known         | known           |

| Microcontroller | unknown      | unknown       | known           |

| Microprocessor  | unknown      | unknown       | unknown         |

Table 1.1. Integral circuit functionality

The complex programmable logic device (CPLD) and the field programmable gate array (FPGA) form a special subset of ASSP. FPGA is an array of 2-6-input logic gates, flip-flops and a set of metal strips, which are interconnected by a large array of programmable bridges. These bridges are formed by MOS transistors, which are controlled by special programming triggers. The routes of the element connections are programmed by the change of the electric field in the gates of the MOS bridges, which mean the origin of the FPGA name. The logic gates are implemented on the base of small ROM. Therefore, any boolean function can be programmed in it. Before the FPGA use, the serial programming stream, called the configuration, is automatically loaded into the FPGA from external ROM. This process is called as the FPGA configuring.

Modern FPGAs include memory blocks, multipliers, fast interfaces, processor cores and other specific units. The logical volume of modern FPGAs

reaches two to four tens of millions of equivalent gates. Sometimes FPGA is part of another ASSP or even heterogeneous multicore system.

Designing complex systems on CPLD and FPGA is cost-effectively and quickly executed. So now the FPGA is often viewed as an alternative to ASIC, especially when a planned series of devices is not more than a hundred thousand units. As a result, each year the number of new projects in FPGA and CPLD is growing, and the number of ASIC projects decreases.

The memory ICs are divided into *the Random Access Memory*, or **RAM**, and *the Read-Only Memory* (ROM).

A system that includes a processor, an application specific processor, RAM, ROM, peripheral devices, etc., which are implemented in a single IC, is usually called as the *System On the Chip* (SOC).

## **1.2.3 Problems**

1) Draw the network of the 3-input NAND gate. How many MOS transistors are used? Why to make the 8-input NAND gate by the similar scheme is not possible?

2) Draw the network of the 3-input NOR gate. How many MOS transistors are used? Why to make the 8-input NOR gate by the similar schema is not possible?

3) Draw the network of the 2-input XOR gate. How many MOS transistors are used?

4) Draw the D-latch network based on the NOR gates. Why the inverters are used in the latches (see Fig. 1.5) but not the NAND, or NOR gates, as in the computers of 70-ies?

5) To measure the gate delay in IC the circular generators are used, which consists of a set of gates, connected to a closed chain. And the odd

number of inverting gates are put in a chain. Explain the principle of such measuring.

6) Let the circular generator, described in the problem 5, consists of 15 inverters. Estimate the inverter delay if the generator frequency is 600 MHz.

7) The design norms are decreased from 45 nm to 22 nm. Estimate, how much the resistance of the 1 mm wire was increased. How much the resistance of the scaled wire bar was increased?

8) To speed up, the processor was overclocked from 2800 MHz to 3200 MHz, and its voltage 1.2 V was increased to 1.32 V. Calculate, how much its speed and power consumption were increased.

9) To save the energy, the processor voltage was decreased from 1.1 V to 0.9 V, but the clock frequency had reduced from 2200 MHz to 1900 MHz. Calculate, how much the processor's speed and power consumption were decreased.

10) How to feed all the triggers of IC to provide the minimum clock skew? Draw the clock signal network for such IC with 30 triggers, when the fanout (load capacity) of the clock buffer is 4 inputs.

11) In the modern IC the signal is faded dramatically at the distance of ca. 0.5 mm. How to provide the signal integrity in the chip of large dimensions?

12) Explain, why FPGA has usually in 3 - 10 times lower clock frequency, than ASIC has.

13) The multiplexers in ICs are usually built on the base of the MOS transistors used as switches. Draw the network of such 2-input multiplexor.

14) Sometimes the trigger cell in IC is built on the base of the distributed capacitance of some bus. Draw the network of such a trigger cell. Explain its properties.

### **1.3. Von Neumann Computer Architecture**

#### 1.3.1 Von Neuman processor structure

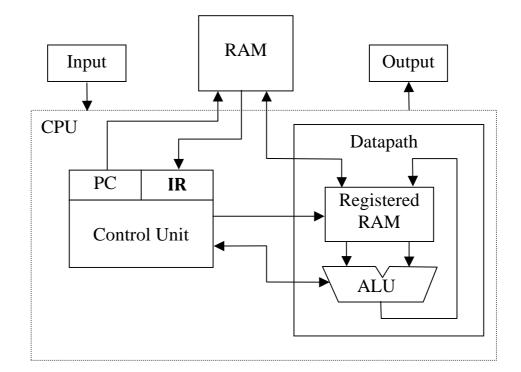

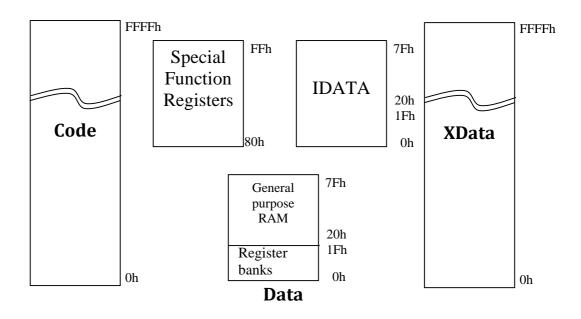

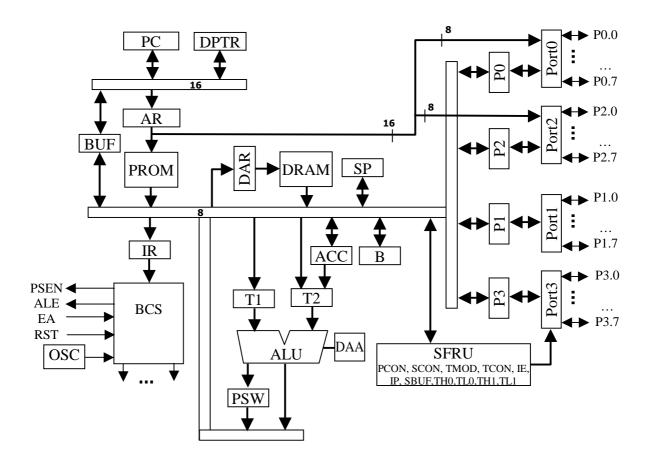

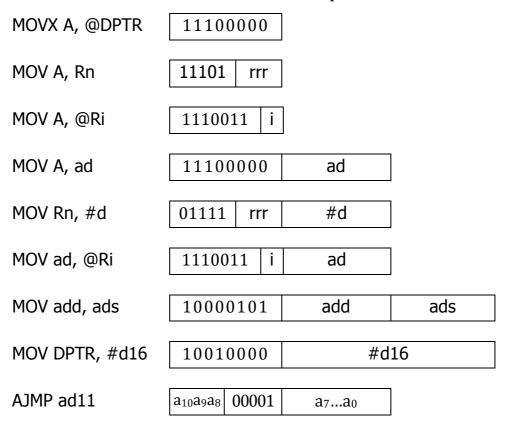

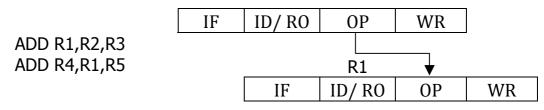

A typical software-controlled computer, which operates on the principle of von Neumann, consists of a control unit, datapath, and RAM. The *control unit* provides the fetching and decoding the instructions, and generating the appropriate control signals. In turn, the datapath consists of registered RAM and an *arithmetic and logic unit* (ALU) (see Figure 1.8.). Often the control unit with the datapath is referred to as the processor core or the *central processing unit* (CPU).

Fig.1.8. Von Neuman processor structure

The *datapath* implements in its ALU the operations, which are coded in the instructions. The *registered* RAM is a set of registers, storing the data, which take part in calculations of an instruction. The **ALU** executes all arithmetic and logic operations, and shift operations, which are coded in the instructions. The initial data and program are loaded through the Input unit, and the results of computations are outputted through the Output unit. Input and Output units are usually formed as a console, which consists of the keyboard and display. The data output can be performed to the tape recorder, printer, etc. as well.

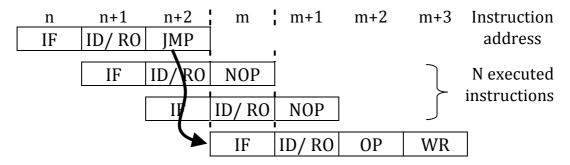

#### **1.3.2 Instruction execution**

During the computations, the von Neumann computer repeats the four-step procedure, executing each instruction.

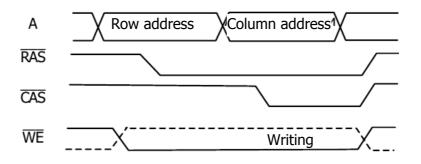

At *the first step*, which is called the instruction fetch, the control unit sends to RAM the instruction address from its *Program Counter* (PC), and a signal that the next instruction is of demand. PC is named as the *Instruction Pointer* (IP) in I80x86 architecture and sometimes called the *Instruction Address Register* (IAR). RAM responds that it sends the read instruction to the control unit, which is stored in the *Instruction Register* (IR).

At *the second step* — the step of decoding — the control unit decides, what kind of instruction is in IR and what action needs to be done to accomplish it. The resulting information is sent to the datapath as the control signals and to RAM as the data addresses.

*The third step* is the step of the instruction operation execution. The datapath reads the necessary data from the registered RAM or from RAM, processes them in ALU and sends the operation flags (zero result flag etc.) to the control unit.

*The fourth step* is the step of storing the results in RAM. Besides, the address of the next instruction is determined and is written into PC register. When the instruction flow is straight, then the next address is derived by the addition of the length of the previous instruction to PC. When the instruction is the branch (jump) instruction then the branch code from the IR register

influences the address in PC. For example, when the condition branch instruction is performed, and the condition is true (for instance, the zero flag is 1) then the displacement code from IR is added to PC.

Each instruction is executed with the same sequence of steps. The processor core repeats these four steps during the execution of the program. The only difference is that each instruction controlls the data fetching and processing differently.

#### **1.3.3 Von Neuman architecture improvements**

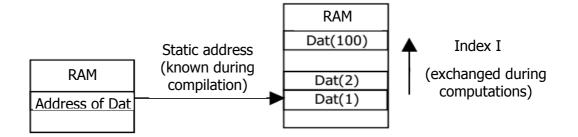

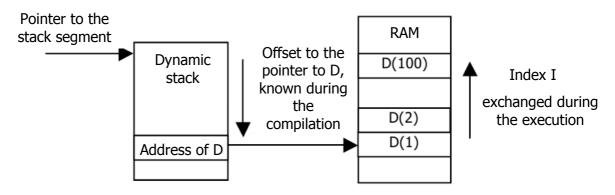

The genuine von Neuman computer model has a set of limitations because it was invented without taking into account the programming experience achieved later. The first limitation is the absence of the facilities for the automatic address modification. Thus, for example, in the array access routine, the data read instruction must be modified by other instructions to index through the array. The resulting *self-modifying code* is very prone to the programming error.

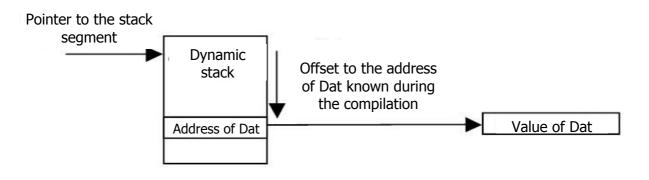

The architecture does not provide the partitioning the instructions and data because no base addressing was involved. Next, the implementation of the input and output units were not clear. The PC register is the separate register without the architectural access, which makes impossible to do the subroutines. Therefore, just after the expansion of the von Neuman architecture, it was modified by different scientists.

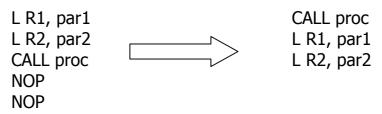

The first incorporation of the index addressing was in the Mark I computer, built in Manchester. The IBM 704, announced in 1954, had already three index registers.

The introducing the standard interfaces provided the attachment to the CPU of a large set of I/O devices in any combination.

But the most prominent improvement was the introduce of the subroutines. This concept was proposed by M. Wilkes, D. Wheeler, and S. Gill. The *subroutine* or *subprogram* is a sequence of instructions that perform a specific task, packaged as a unit. This unit can then be used in programs wherever that particular task should be performed. The subprograms may be defined within programs, or separately in the libraries that can be used by multiple programs.

A subroutine is usually coded so that it can be started (*called*) several times and from several places, including from other subroutines, and then branch back (*return*) to the next instruction after the call instruction, once the subroutine's task is done. A subroutine call not only branches but saves the contents of the PC somewhere. A return retrieves the saved contents of the PC and places it back in the PC, resuming sequential execution by the instruction following the subroutine call.

The advantages of programming with the subroutines include:

- decomposing a complex programming task into simpler steps;

- reducing the duplicate code within a program;

- enabling the reuse of codes across multiple programs;

- dividing a large programming problem among various programmers.

#### 1.3.4 Functions implemented in the processor

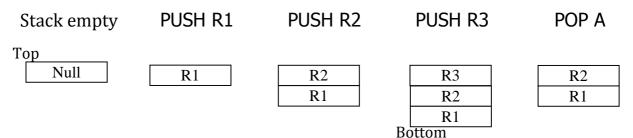

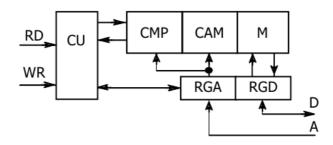

All the functions described in the paragraph 1.3.3, are performed in the data processing unit and the control unit. These functions are categorized according to their purpose as the following.

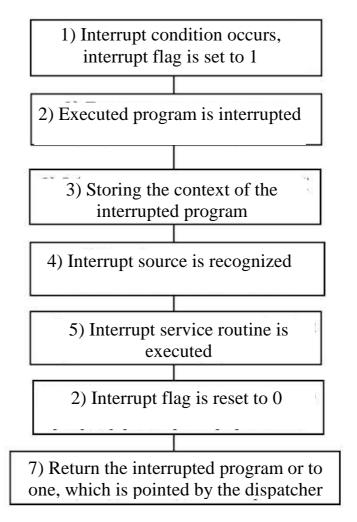

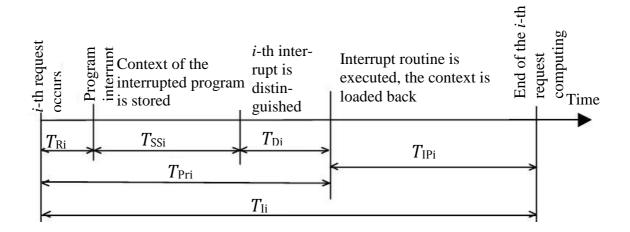

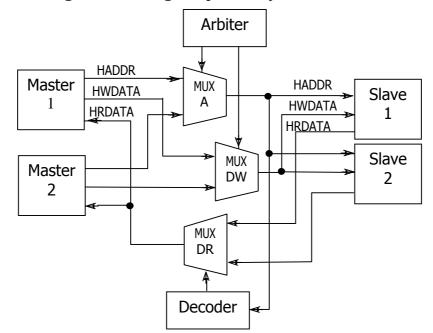

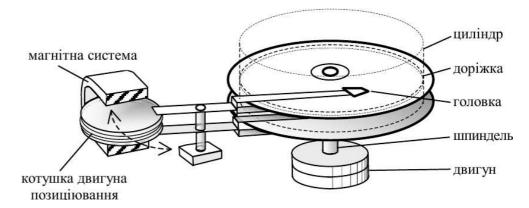

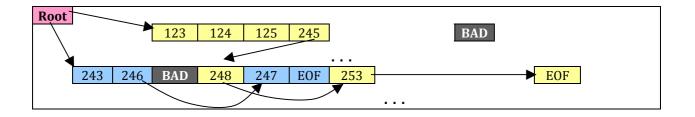

*The instruction fetch functions* control the flow of instructions in the processor. They provide the next instruction fetch (calculating its address)