A.M. Sergiyenko

# **Computer Architecture**

# Part 2. Parallel Architectures

Kyiv-2016

| CONTENTS                                                     | 1   |

|--------------------------------------------------------------|-----|

| ABBREVIATIONS                                                | 3   |

| 3 PARALLELISM OF                                             | 6   |

| SINGLE-PROCESSOR COMPUTERS                                   | 6   |

| 3.1 Pipelined and vector data processing                     | 6   |

| 3.2. Vector pipelined computers                              | 16  |

| 3.3 Superscalar processors                                   | 21  |

| 3.4. Methods of superscalar processor performance increasing | 25  |

| 3.5. Multithreading                                          | 35  |

| 3.6. Memory access parallelism                               | 39  |

| 4. MULTITASKING AND DATA PROTECTION                          | 47  |

| 4.1. Virtual memory                                          | 47  |

| 4.2. Computer multitasking                                   | 52  |

| 4.3 Memory protection                                        | 55  |

| 4.4. Memory management in the IA-32 architecture             | 58  |

| 4.5. Virtual memory of the IA-64 architecture                | 69  |

| 4.6. Problems                                                | 71  |

| 5. MULTIPROCESSOR ARCHITECTURE                               | 73  |

| 5.1. Fundamentals of multiprocessor architectures            | 73  |

| 5.2. Processors with the SIMD parallelism                    | 89  |

| 5.3 Multiprocessor Architectures                             | 97  |

| 5.4 Graphics accelerator architecture                        | 108 |

| 6 APPLICATION SPECIFIC PROCESSORS                            | 111 |

| 6.1 Introduction                                             | 111 |

| 6.2 Microcontrollers                                         | 112 |

| 6.3 DSP microprocessors                                      | 119 |

|--------------------------------------------------------------|-----|

| 6.4 Processors with hardware control. Configurable computers |     |

| 6.5 System on chip in FPGA                                   |     |

| 7 COMPUTER ARCHITECTURE PROSPECTS                            | 132 |

| LIST OF RECOMMENDED LITERATURE                               | 137 |

| ANNEX 1                                                      | 139 |

# ABBREVIATIONS

- ALU arithmetic and logic unit

- APIC Advanced Programmable Interrupt Controller

- ARM Acorn (Advanced) RISC Machines

- AS Architecture State

- BHT Branch History Table

- BTB Branch Target Buffer

- CISC complex instruction set computer

- COMA Cache-Only Memory Architecture

- CPL Current Privilege Level

- CPU central processing unit

- CRC Cyclic Redundancy Check

- CUDA Compute Unified Device Architecture

- DMA Direct Memory Access

- DPL Descriptor Privilege Level

- DRAM Dynamic Random Access Memory

- DRIS Deferred scheduling register Renaming Instruction Shelf

- DSMA Distributed Shared Memory Architecture

- DSP Digital Signal Processing

- GDT Global Descriptor Table

- GPIO General Purpose Input-Output

- GPU Graphic Processing Unit

- HDD Hard Disc Drive

- HSA Heterogeneous System Architecture

- IA-32 32-bit Intel architecture

- IDT Interrupt Descriptor Table

- IoT Internet of Things

- IP Instruction Pointer

- ITLB Instruction Translation Lookaside Buffer

- I2C Inter-Integrated Circuit

- JTAG Joint Test Action Group

- LDT local descriptor table

- LP Logical Processor

- MCM MultiChip Module

- MIMD Multiple Instruction flows Multiple Data flows

- MIPS million instructions per second, microprocessor without interlocked pipeline stages

- MFLOPS mega floating point operations per second

- MMU Memory Management Unit

- MMX MultiMedia extension

- MPI Message Passing Interface

- MRMW Multiple Readers Multiple Writers

- MRSW Multiple Readers Single Writer

- MT mode Multi-Task mode

- MTA Multi-Threaded Architecture

- NUMA Non-Uniform Memory Access architecture

- OpenCL Open Computing Language

- OS Operational System

- PC Program Counter, Personal Computer

- PKR Protection Key Register

- PRAM Parallel Random Access Machine

- PU Processing Unit

- PVM Parallel Virtual Machine

- RAM Random Access Memory

- RAS Row Address Select, Return Address Stack

- RAT Register Alias Table

- RID Region IDdentifier

- RISC Reduced Instruction Set Computer

- ROM Read-Only Memory

- RPL Request Privilege Level

- SAXPY Single precision A multiplied by X Plus Y

- SIMD Single Instruction flow Multiple Data flows

- SIMT Single Instruction Multiple Threads

- SM Streaming Multiprocessor

- SMP Symmetric MultiProcessor

- SMT Simultaneous MultiThreading

- SoC System on a Chip

- SPI Serial Peripheral Interface

- SPMD Single Program Multiple Data

- ST mode Single-Task mode

- T-cache Trace cache

- TLB Translation Lookaside Buffer

- TR Task Register

- TSS Task State Segment

- UART Universal Asynchronous Receiver-Transceiver

- UMA Uniform Memory Access architecture

- VLIW Very Large Instruction Word

- VPN Virtual Page Number

- VSMA Virtual Shared Memory Architecture

- $\mu op micro-operation$

## 3 PARALLELISM OF SINGLE-PROCESSOR COMPUTERS

#### 3.1 Pipelined and vector data processing

#### 3.1.1 Basic types of parallelism in computers

The main feature of the von Neumann computer architecture reviewed above is the inseparable implementation of all actions. This means that all the instructions and microinstructions are indivisible and are strictly implemented in sequence. The instruction inseparability or atomicity means that its implementation cannot be slowed down and another action be performed during this situation with some elements of the memory. For example, the following instruction could not start running before the end of the previous instruction, the datum is read by the running instruction from RAM strictly after it was written there by the previous instruction A set of instructions can not be executed in several ALUs, i.e. in parallel. Therefore, the speed limit of the von Neumann processor is determined by the period of the instruction execution. It is limited by the amount of delays of instruction decoder, ALU, program RAM, data RAM.

In this section, the architecture details are considered, which help to do without the action atomicity and to speed up the computation due to the parallelization. First, some principles of the computer design are recalled.

*The parallel processing principle*. To achieve the high performance and (or) the reliability of computer computations, the independent control or calculation steps are distributed among several operating and control machines (or CPUs), which are connected through some switching system.

*The pipeline processing principle* of information means that complex operation sequence is divided into several successively performed steps

(micro steps) so that they can be performed in parallel for the flow of such operations.

A few definitions are added:

**Parallelism** is an ability of simultaneous execution of independent arithmetic and logical operations or service. There are three main forms of parallelism:

— natural or vector parallelism;

— parallelism of independent branches;

— parallelism of related operations or scalar parallelism.

The essence of the *parallelism of independent branches* is that the independent software branches can be allocated in a program which solves the large problems, which are processed in parallel.

Under *natural parallelism*, the ability to process the independent data by the same algorithm is understood above all. This is, for example, the ability of simultaneous processing the elements of data vectors (*vector parallelism*), performing a number of identical or similar tasks for different sets of input data.

The program for the von Neumann machine is a list of operations performed in series. The *scalar parallelism* means that the subsets of these operations can be performed in parallel if there are no dependencies between them.

*Synchronization act* is a moment of time, when a portion of calculations transfers the control to other portions, such as the moment, when an instruction passes the control to another one, a computational process activates another one, a subroutine sends the results and calls the next one for execution.

*Computation grain* is the average time period between adjacent synchronization acts in the parallel computing, or the synchronization period.

Regarding the scalar parallelism, the term *fine-grained parallelism* (synchronization period is 1 - 100 clock cycles of CPU) is often used. This is different from the *medium-grained* (about  $100 - 10^5$  clock cycles) and *coarse-grained parallelism* (approximately over  $10^5$  cycles). The medium-grained and coarse-grained parallelism usually consider the vector parallelism and the parallelism of independent branches, respectively.

Each type of computer architecture can effectively perform only those algorithms, that have inherent granulation of computations. Next, the architecture of pipelined RISC-processor is considered that implements the fine-grained parallelism at the microarchitecture level.

#### 3.1.2 RISC-processor instruction pipeline

The main point for the development of pipelined computers was the justification of the method which was called "the water pipeline principle" by the academician S. A. Lebedev in 1956. First of all, the instruction pipeline was implemented, on which the Soviet computer  $E_{PCM}$ -6 (1957 – 1966) and English machine ATLAS (1957 – 1963) were built almost simultaneously.

The instruction pipeline made it possible to get the performance of 1 million operations per second in the computer E9CM-6. Further, the instruction pipeline was improved and became an essential element of all high-speed computers, such as computers IBM/370 and EC10xx.

Since the mid-80s of the last century, all microprocessors were built on the RISC-microprocessor architecture, which instruction pipeline is a characteristic feature.

The RISC architecture was considered above in terms of its instruction set. Recall that one of the principles of the RISC-processor design is the implementation of a single instruction in one clock cycle. This principle becomes possible through the pipelined instruction execution.

By the pipelined instruction execution, the instruction implementation is divided into a specific sequence of separate phases. This division into phases is implemented in the architectures in different ways. But in general, this division is as follows:

— instruction fetching (IF). Loading instructions from the instruction memory into the instruction register of the processor core;

—instruction decoding (ID). Due to the simplicity of the RISC instructions, ID is very fast;

— reading the operands (RO). Because the operands are often found in the register memory of the RISC-processor, RO is very fast;

— operation (OP). It is actual instruction calculating;

— writing results (WR) back in registers or other memory.

If the sequence of instructions is executed without conditional branches, the phases of these neighboring instructions can be performed in parallel instruction pipeline stages, as shown in Fig.1.22.

Because the instruction format is simple, its length (32 bits) is known, the instruction fetching is simple. CPU reads the instruction words from memory without the need to determine the length of the instruction, as in the case of the CISC processor. The instruction decoding is also simplified, as the number of the instruction formats is minimized, the opcode, operand and address fields are always in the same position of the instruction word.

The instructions are divided into a set of instructions addressing RAM and a set of arithmetic instructions. This simplifies the RO phase. In the arithmetic instructions, the operand reading occurs only from the register memory and is usually performed by the direct addressing.

Due to the fact that all instruction phases are of nearly the same complexity, they are usually performed in the instruction pipeline. For example, a piece of the program

ADD R1, R2, R3; R1=R2+R3 — instruction 1 ADD R4, R5, R6; — instruction 2 ADD R7, R8, R9; — instruction 3 ADD R10,R11,R12; — instruction 4

is performed as follows. As the instruction 4 selected, the instruction 3 is decoded and its operands are selected for the instruction 2, which performs addition, the result of the instruction 1 is written in the register R1 (see Fig 1.22). Although the implementation of a single instruction takes four cycles, the average processor performance is approaching to one instruction per clock (with a continuous stream of independent instructions).

In the previous example, all the instructions are independent. A special example occurs, when the neighboring instructions depend on data:

ADD R1, R2, R3; R1=R2+R3 — instruction 1 ADD R4 ,R1, R6; — uses R1, writes R4 ADD R7 ,R4, R9; — uses R4, writes R7

In this program, each instruction needs the result of the previous instruction. According to the instruction pipeline phases, it is impossible, since the phase of read and write of neighboring instructions are mismatched (Fig. 1.22). But this problem is solved through a method of the *result forwarding*. During this computations, the instruction result is sent immediately as an operand for the next instruction, as it is shown in Fig. 1.23.

The instructions which are downloading data and saving them in RAM are different from the ALU instructions, that actually the data reading lasts not for one but for several cycles due to low performance of RAM and its connection through the interface.

For example, the addition instruction in the next program piece

L R3, OPER ADD R4, R3, R2

can not be performed in the next clock cycle after the operand OPER reading because it is implemented for more than one clock cycle, for example, for 2 (if RAM is a cache memory). But if the NOP instructions are inserted between instructions:

L R3, OPER NOP ADD R4,R3,R2

it increases the delay between the instructions in one clock cycle, which guarantees the timely appearance of the operand OPER in a register R3. These NOP instructions are usually inserted automatically by the compiler.

Often the compiler rearranges the instructions so as to minimize the number of additional NOP instructions, such as:

| Initial program | Program after optimization |

|-----------------|----------------------------|

| L R2,OP1        | L R2,0P1                   |

| L R3,0P2        | L R3,OP2                   |

| NOP             | L R5,OP3                   |

| ADD R4,R2,R3    | L R6,OP4                   |

| L R5,OP3        | ADD R4,R2,R3               |

| L R6,OP4        | ADD R7,R5,R6               |

| NOP             |                            |

| ADD R7,R5,R6    |                            |

After this instruction reshuffle, the program meaning remains the same. But the delay between the operand reading from RAM and use them in the arithmetic instructions is permissible, so the NOP instruction insertion is not required.

The real programs contain a large number (approximately 25%) of conditional and subroutine call instructions. These instructions implementation has two aspects. First, in the cycle, when the processor recognizes the following instruction, the instruction that is following it (placed at the following address) is already in the pipeline and begins to be handled. Second, an instruction that really needs to be done after the branch instruction, cannot enter the pipeline immediately in the next cycle. So the pipeline needs to be stopped and be cleaned from the instructions that should not be implemented.

The easiest way to speed up the instruction execution is the method of the *delayed branch*. Thus when the branch instruction is recognized, the

opportunity is given to one or more instructions running in the pipeline, before the branch itself is done.

Consider the following sequence of instructions:

L R9, #0 JMP M1 ADD R9, R9, #1 ... M1: ADD R9, R9,#1

When the JMP instruction goes to the pipeline, the instruction ADD is already in the pipeline and it starts to be executed. When the branch to label M1 is actually made and the second instruction ADD is done, the number 2, but not the number 1 occurs in the register R9, as it would be when the program is running in the normal von Neumann processor.

A method of placing and performing the instructions after the branch instruction is called as the **branch delay slot** method. This method helps to the compiler to minimize the NOP instructions. For example, the parameters, which are transmitted to the routine, can be loaded by instructions placed after the CALL instruction.

| Initial program               | Program after optimization |

|-------------------------------|----------------------------|

| L R3, OP1<br>CALL SUBR<br>NOP | CALL SUBR<br>L R3, OP1     |

The first subroutine instruction that is called can be put in the delayed branch slot as well. Then the call address is increased to this instruction length to "circumvent" this instruction during a call.

The programming of the delayed branch is an unusual thing for a programmer. But it is quite clearly and correctly performed by a compiler. Thus, the compiler for the MIPS architecture is able to rearrange the instructions in the program to fill 70 to 90% of the delayed branch slots.

#### **3.1.3 CISC processor instruction pipeline**

Modern CISC processors also have the instruction pipelines, through which they achieve high clock speed. Consider for example the evolution of the instruction pipeline of processors Intel Pentium, ..., Pentium-4, which are synonymous of P5, P6, P7.

The structure, or more precisely, the microarchitecture of the P5 processor has a five-staged instruction pipeline with the stages: instruction sampling, two stages of the decoder, operation stage and writing the result. This made it possible to have a clock speed of about 100 MHz.

In the microarchitecture P6 (PentiumPro, Pentium II, Pentium III), the instruction pipeline performs both RISC and CISC instructions, but the last instructions are performed ineffectively. It has the enlarged pipeline with 12 stages. Through the pipelining and modernized ASIC technology, the clock speed was increased to 1.4 GHz.

In the P7 microarchitecture while performing the CISC-instructions they are replaced dynamically by the chains of RISC-instructions, which are executed in the pipelined mode (see. hereinafter the "trace cache"). Thus, the reading and converting the CISC- instructions to the RISC-instructions is performed in 8 pipeline stages, and the RISC-instructions are implemented in 20 stages. This, Pentium-4 in 2005 reached a clock speed of 3.8 GHz. An interesting detail of this microarchitecture is the fact that two of the 28 pipeline stages generally do not perform any computations. They are intended to equalize the signal delay during the data transfer from one part to another part of the chip. This is because the area of the CISC-chip is too large to send signals through it without the data buffering and pipelining.

Another shortcoming, which was found in this architecture is a great delay of the pipeline flush during the unpredicted branch (see "Conditional branch predictions"). The performing reading the RAM after the recent

writing to it causes a huge pipeline slowdown as well (see "Memory access consistency").

Thus, the CPU clock speed is not a reliable indicator of the processor performance with a particular architecture. The instruction pipeline stage number should be chosen so as to ensure the maximum performance of the microarchitecture (eg, solving the test problems) at the maximum clock frequency that is acceptable to it. Unlike CISC-processors, RISC-processors have a smaller chip area and a shorter instruction pipeline, so they have a higher clock speed and higher overall performance and less power consumption.

#### 3.1.4 Software pipelining

When hardware pipelining, the instruction implementation is divided into stages, such as instruction fetching, execution, and writing. But the processor executes a single instruction per clock cycle only after filling the pipeline.

Similar processes occur in the software pipelining. By it, a single loop of the loop nest is divided into S stages, such as data reading from RAM, intermediate result calculation and data writing in RAM. Then the first stage of the *i*-th iteration is executed, the second stage of the *i*-1-st iteration is, etc. in a single program loop. This loop is arranged in the way, that the instructions of the pipeline filling are placed before the loop and the flushing instructions are placed after it. Below is a program example of adding two arrays with the program pipelining.

Initial program (11 cycle iteration)

After optimization (8 cycle iteration)

- L R2, ARRA ; array A address

- L R3, ARRB ; array B address

- L R4, #(N\*4); array length

- L R5, #4 ; address increment

- L R2, ARR1 ; array A address

- L R6, [R2] ; loading A(0)

- L R3, ARRB ; array B address

- L R7, [R3] ;loading B(0)

R4, #(N\*4); array length M1: L R6, [R2] ; loading A(i) L R5, #4 ; address increment L R7, [R3] ; loading B(i) L M1: ADD R3,R3,R5; address modific. NOP R7, [R3]; loading B(i+1) NOP L ADD R8, R6, R7 ;A(i)+B(i) ADD R6, R6, R7; A(i)+B(i)R6, [R2] ; sum storing R6, [R2] ; sum storing S S ADD R2,R2,R5; address modific. ADD R2, R2, R5 ADD R3,R3,R5; address modific. SUB R4,R4,R5 SUB R4,R4,R5 ; end of iteration? JNE M1; JNE M1 ; jump to cycle L R6, [R2]; loading A(i+1) NOP

Often, the software pipelining is used in the floating point calculations, when the latent delay of the pipeline is very large (more than 6-8 cycles). It is widely used in the signal microprocessors, and in VLIW-microprocessors, which execute plenty of parallel actions in a single instruction cycle.

#### **3.1.5 Problems**

1) Estimate the granularity of computations in your PC at the intruction level.

2) Estimate the granularity of computations in your PC at the level of the OS function calls.

3) Estimate the granularity of computations using the Web service and TCP/IP protocol.

4) The RISC program contains 25% of branch instructions. The instruction pipeline has 5 stages. Estimate the average program speed in instructions per clock cycle when the branch delay slot method is not used.

5) In the RISC processor, the data reading from RAM lasts 3 clock cycles, the program contains 25% of data loading instructions. Estimate the speedup of the program when the NOP instructions after the loading instructions are removed during the program optimization.

#### **3.2. Vector pipelined computers**

#### 3.2.1 Vector parallelism algorithms

In the algorithms of the structured data processing, the vector operation that has the natural parallelism is the most common. The *vector* is a one-dimensional array with a size, that is known at compile time. Often a vector is formed from a multidimensional array. In the sequential languages, such as Fortran, some vector operation is expressed by the DO cycle:

DO 10 I = 1,N 10 C(I) = A(I) + B(I+16);

The vector operations like addition, multiplication, division, comparison, etc. are universal in nature and often are included in the parallel programming languages. The vector operation, given above by a cycle, is represented in the MATLAB language more clearly:

C = A (1: N) + B (16: N + 16);

The areas of the vector use are operations on large arrays, digital signal and image processing, linear algebra problem solving, modeling physical environments, meteorology, optimization, design automation, etc.

#### 3.2.2 Arithmetic pipeline

In the late 60's, the arithmetic pipeline was introduced into the processor datapath. It has become the central device in the supercomputer CRAY-1 (1976). The *arithmetic pipeline* has the multistaged structure, each stage performs a single micro-operation for the data stream calculating. Then, a set of data is processed in this pipeline but in the different stages.

This arithmetic pipeline enables to efficiently compute the vectors of numbers, but during the processing of the separate numbers, the most of its stages are idle, which is shown below. The supercomputers usually solve the numerical problems using floating-point double precision data. Such operations can be divided into several dozens of micro-operations, which are performed in the respective stages. As a result, such a pipeline has the maximized clock frequency up to several gigahertz. Therefore, it possible to obtain the performance of the arithmetic pipeline up to several hundreds of millions floating point operations per second, i.e. hundreds and thousands *MFLOPS* (Mega Floating Point Operations Per Second).

The majority of supercomputers in 70–80s and early 90s were the vector pipelining computers. But then they did not survive the competition with the multiprocessor computers.

The floating-point ALU of the modern microprocessors is usually the arithmetic pipeline. The floating point signal microprocessors and graphic coprocessor can be classified as the vector-pipelined computers as well. Therefore, the specialists should closely examine the properties of the vector pipelining architectures.

#### 3.2.3 Vector pipelining architecture

The *vector pipelining* computers have a special architecture, which is adapted to perform the vector operations. The features of this architecture are the following:

— a set of arithmetic pipelines to perform operations of addition, multiplication, division, floating point, and others;

— vector memory, which is analogous to the register memory, in which a cell serves to store a single vector (usually 64 words);

— sliced RAM; *N* blocks of this RAM allow the computer to access *N* adjacent cells of a single vector simultaneously;

— hardware devices to generate the address sequences of the vector elements (*address generator*);

— ability to connect the output of one arithmetic pipeline to the input of another one to perform a single group operation or a set of neighboring arithmetic instructions on the same data without writing the intermediate results in RAM (*pipeline concatenation*).

The typical *group operation* is an SAXPY (Single precision A multiplied by X Plus Y) instruction, which performs the action A \* X + Y on the single precision floating point vectors. By its implementation, the multiplication and addition pipelines are concatenated.

Vector pipelining computers are subject to the pipelining principle. The principle is that the calculation of complex function is divided into a number of successive steps performed by the computing resources, called stages. Moreover, the data flow is throughput consistently these stages and due to the continuous flow, these data are processed in parallel, and adjacent data are processed simultaneously on adjacent levels. Through the pipeline stage specialization, and increasing the number of these stages, both the clock frequency is increased to the extremal values and the hardware costs are minimized.

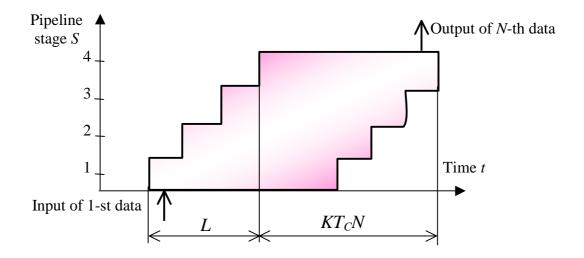

Fig. 3.1 shows a timing diagram of a pipeline loading when it performs the vector operations for the vector of the length *N*. the diagram shows that the vector operations are associated with the time overhead. According to Fig. 3.1, the performance of a vector operation can be estimated by the formula:

$$T = L + kT_c N, (*),$$

where  $T_c$  is the clock interval, k is the average number of cycles for a single result, i.e. the period of computations, L is the pipeline startup, i.e., the time

required to fill the pipeline, including time for preparation of vector operands. In the simplest case, it can be estimated as  $L \approx SkT_c$ .

Fig. 3.1. Time diagram of the pipeline loading

Typically, the value *L* is larger for computers, in which the vectors are usually stored in RAM than for computers with the frequently used vector RAM.

The period  $kT_c$  for the result calculating is associated with the data input period. Many computers have k = 1 and this period coincides with the period of the clock. In the high-performance computers with several pipelines, such as a modern graphics accelerators, the number of pipelines *M* can reach from tens to thousands, and then, at the maximum load of them, this figure reaches k = 1/M.

From the formula (\*), it follows that the average duration of obtaining a single result is equal to

$$T_R = kT_C + L/N.$$

The performance of the pipelined computer could characterize the number of results that it produces per unit of time:

$$R = \frac{1}{T_R} = \frac{N}{kT_C N + L}.$$

(\*\*)

If L = 0 or when  $N \to \infty$ , then R approaches to  $R_{\infty} = 1/(kT_c)$ . This value is called as an *asymptotic performance*. It is the maximum performance with no overhead of the running pipeline. If N = 1, we obtain the minimum performance that is significantly less than the performance of the conventional scalar computer.

The value  $N_{\frac{1}{2}}$  of the *half performance length* is of the interest. It equals to the length of the vector, for which the computer reaches a half of the asymptotic performance. Let  $kT_c = 1$  ns, L = 40 ns. Then, according to (\*\*),  $R_{\infty} = 10^9$  Flops, and

$$\frac{10^9}{2} = \frac{N_{\frac{1}{2}}}{10^{-9}N_{\frac{1}{2}} + 40.10^{-9}}$$

then solving this equation gives  $N_{\frac{1}{2}} = 20$ .

Assuming that  $L \approx SkT_c$ , i.e., the number of pipeline stages for this example is S = 40, one can reach the following conclusion. If the length of the vector is less than a half of the number of pipeline stages, then the pipeline computer performance is less than a half of the asymptotic performance. This finding should be taken into account when the vector data are processed in modern processors.

#### 3.2.4 Problems

1) One program for the vector pipelined computer performs multiplication of 64-component vectors, and then adds the result to another vector. Another program does the same but using the group operation. Estimate the speed-up of the second program if the pipeline length is equal to 30.

2) Solve the problem 1, when the vector length is equal to 1000.

3) Solve the problem 1, when the vectors, which are stored in the outer RAM, the pipelined access to it lasts 250 clock cycles.

4) The pipeline length is 32. What is the vector length to achieve 80% of the asymptotic performance? How many times is it longer comparing to the half performance vector?

5) The graphic accelerator has the pipeline length of 400. What is the half performance vector length for it? How degrades the performance, when the vector length is equal to 64 comparing to the asymptotic performance?

#### 3.3 Superscalar processors

#### 3.3.1 Superscalar architecture

The von Neumann architecture was almost always the leading one by the computing expanding. The appearance of each new computer generation can be caused by the attempt to expand the bottleneck of this architecture. This bottleneck is formed by the communication link between the instruction and data memory, and the CPU core.

Thus, the cache RAM was built in the i486 microprocessor. This enables the CPU core to perform simultaneous reading 16 bytes of instructions, write and read 4 bytes of data to/from the cache RAM. This flow of information between the core and the cache RAM became five times greater than the flow between CPU and the main RAM.

A new step of the von Neumann architecture began with the advent of the superscalar processors. The main feature of the superscalar architecture is simultaneous fetching of multiple instructions from the cache RAM, their decoding, and distribution them to multiple instruction streams, that are executed in the separate blocks. The terms of such parallel instruction execution are:

the adjacent instructions should be independent on the data, addresses, and control;

2) free hardware resources should be assigned to the instructions for their implementation.

So, the superscalar processor can simultaneously run multiple instructions in several execution blocks. In other words, it implements the scalar parallelism at the microarchitecture level.

Another feature of the superscalar architecture is the separation of instruction cache RAM from the data cache RAM, providing the parallel access to both data and instructions. It also expands the von Neumann architecture bottleneck. Thus, the Pentium superscalar processor increases the throughput between the CPU core and cache RAM in three times compared to the i486 processor a the expense of such a separation.

The third feature of the superscalar processor is that it has sufficient operational resources and equipment to detect the neighboring instructions that can be performed simultaneously.

The superscalar architecture set except IA-32, IA-64, and their clones include the architecture families named Power PC, SuperSPARC, PA-RISK, IBM Power, MIPS, ARM and others. Now, these processors have up to six instruction streams.

Consider for example the SuperSPARC architecture. Specialists of the SUN Microsystems company determined the frequency of the instructions in the typical problems that are solved in the SPARC systems (see Table. 3.1). Analysis of the instruction statistics in Table 3.1 shows the feasibility of division the instruction stream into three parts: fixed-point arithmetic instructions, floating point instructions, RAM addressing instructions. And this division is implemented in the SuperSPARC processor. Thus a group of

four neighboring instructions is fetched from the cache RAM simultaneously. From this group, no more than three instructions are selected.

| Instruction type          | Application with integer data | Application with floating point data |

|---------------------------|-------------------------------|--------------------------------------|

| Fixed point arithmetic    | 50%                           | 25%                                  |

| Floating point arithmetic | 0                             | 30%                                  |

| RAM reading               | 17%                           | 25%                                  |

| Writing in RAM            | 8%                            | 15%                                  |

| Conditional jump          | 25%                           | 5%                                   |

Table 3.1. The instruction frequency in various applications

These instructions meet the following conditions. There must be no more than:

— two instructions giving integer results;

— one instruction addressing the data RAM;

— one floating point instruction;

— one control and branch instruction that has to be the last in the group.

Measuring SuperSPARC CPU performance showed that, on average, it simultaneously executes from 1.4 to 2 instructions at the peak of 3 instructions.

The development of superscalar architecture towards increasing the number of instruction streams is associated with the increasing of the complexity of the logic circuits, which recognize the independent instructions in the instruction flow. On the other hand, the possibility of the scalar parallelism for any practical problems is limited. Therefore, it is inappropriate to increase the number of streams exceeding six to eight.

The superscalar processors parallelism is limited by:

— scalar parallelism level existing in the program. The average parallelism level in usual programs is from 2 to 3 instructions;

hardware resources, now up to ten instruction streams can be realized;

— parallelism detection unit complexity.

To improve the superscalar processor performance can be fulfilled in the following ways:

— increasing the superscalar parallelism in the program by using the appropriate programming techniques and compiler to increase parallelism at the instruction level;

— to perform automatically the instruction overlap increasing during the instruction stream decoding;

— to specify the parallelism explicitly in the compiled program to facilitate the parallelism recognition in the hardware equipment;

— to perform two or more independent software processes to increase the number of independent instructions in the stream (multithreading);

reducing the instruction pipeline stalls, for example, to foresee the conditional branches;

— reducing the pipeline depth, so the pipeline is filled more quickly, and the data dependence cycles are shorter (calculating the result D, writing D in memory, reading D for calculations).

#### 3.3.2 VLIW-architecture

Another way of implementing parallelism at the instruction level is the processor architecture with a long instruction, i.e., VLIW-architecture (Very Large Instruction Word). The long VLIW-instruction contains multiple independent fields, which control the different operating units.

If we assume that the superscalar processor performs strictly the same number of instructions, even empty ones, in each cycle, we get the VLIWprocessor architecture.

Compared to the superscalar processor, the instruction stream from the program RAM is increased in the VLIW-processor, but there is no need for recognition of the independent instructions. Both the programmer and the compiler are responsible for the VLIW-processor loading.

Some signal microprocessors can be attributed to VLIW-processor, for example, SHARC. Intel Itanium microprocessor architecture has the architecture EPIC (explicit parallel instruction computer), which is a VLIW-architecture with 16-byte instruction word length, three instructions per word.

#### 3.4. Methods of superscalar processor performance increasing

#### 3.4.1 Conditional branch prediction

When performing a conditional branch instruction, the next instruction is either the instruction that is already in the pipeline, or the instruction, which address is specified in the branch instruction. In the latter case, the instruction pipeline must be flushed.

The branch instruction execution has the unequal probability of its branches. If the instruction from the most probable branch is loaded into the pipeline the need for the pipeline flush occurs much less frequently, and the CPU speed is much higher. To realize this feature, the mechanisms of the conditional branch prediction are involved in the superscalar processors.

The most common branch, that requires foresight, is a branch instruction for the verification of a program cycle end. Thus the probability of a return to the beginning of the cycle is close to unity.

Such an instruction can be detected in compilation time. In the first RISC-processors, in which the prediction mechanism was involved (IBM Power), the compiler was setting a flag in the branch instruction, which assigns the probable branch direction.

In modern processors, the prediction is performed by the special equipment during the program execution in accordance with some strategy. To predict the branch address, the Branch Target Buffer (**BTB**) is used. This table operates as a cache RAM and stores the addresses of instructions to which the branches are done previously. For example, the processor Pentium-4 has BTB with a size of 4096 elements.

To predict the direction of the conditional branch, a mechanism is used, which is based on studying the behavior of branches in the program during its execution. This mechanism takes into account both a local behavior of branches (such as "usually jumps," "typically does not jumps") and a global law ( "is changed with a particular law", etc.). The history of these branches is written in a special Branch History Table (**BHT**).

Current prediction algorithms implemented in hardware ensure the correct predictions by more than 90%. In the perfect prediction systems, the following prediction algorithms are used:

— combination of local and global mechanisms for predicting usual branch instructions considering the history of their behavior;

— static prediction for the instructions that are performed the first time, based on empirical relations. For example, "jump back" is assumed to be made, because the branch can start the cycle, and "jump forward" is assumed as undone;

— prediction of short cycles, which detects a jump at the end of a short cycle and calculates the number of iterations of the cycle, allowing correctly predict the moment of time of the cycle release;

— prediction of an indirect branch, i.e. a branch to the address in the memory cell, defining of target addresses for various instruction results even with the alternating program behavior;

— prediction of the target address of the Return instruction. It utilizes a special hardware stack for the return addresses, called as a Return Address Stack (RAS) for testing instructions Call — Return.

The branch prediction unit operates with the instruction decoder in parallel and independently from it. Through the effective implementation of the foresight of the branch address in the processors Pentium-III, Pentium-4 and K8 with proper prediction, they loose averagely only one clock cycle for the branch instruction execution. This means that the minimum time overhead, for example, to perform the iteration cycle or one jump in the chain of branches is equal to two cycles. In fact, the prediction in this chain of executed instructions runs in its own cycle, which consists of two stages: prediction and reading a new line of bytes from the instruction cache RAM and decoding the instructions from this line.

When an instruction enters the execution pipeline stage, it is clarified, whether this branch is truly predicted or not. At the time of this instruction completion under the wrong prediction, the execution of all following instructions is canceled and the reading instructions from the cache RAM for the true address is started.

This procedure is called a *pipeline flushing*. The time (in cycles) on the instruction branch execution beginning with its reading from the cache RAM is called the *unpredicted branch pipeline length*. This time is characterized by the time losses in the ideal conditions when the instruction goes through all the pipeline stages and is never delayed due to external causes (interrupts, cache misses, etc.). The unpredicted branch pipeline length takes the value of

11 cycles for Pentium-III to 30 cycles for Pentium-4E. In the real conditions, the losses of improperly predicted branches can be higher.

### 3.4.2 Trace cache and cycle unrolling

The instruction cache RAM of the processors like Pentium-4 differs from the Instruction cache RAM (I-cache) of the predecessor processors. A lot of instructions read from the external RAM in it are recoded to other instructions or sets of micro-operations ( $\mu$ ops) before writing to the cache RAM. Therefore, not separate instructions but the sequences of instructions or  $\mu$ ops are distinguished in this cache RAM. These sequences are called as traces, and the cache RAM is called as Trace cache (T-cache).

The *trace* is a sequence of instructions or µops that perform the same actions as is specified in the program portion. The traces are formed in accordance with the dynamic order decoded instruction flow. At the time of decoding, the initial branch prediction is performed. And if the expected branch is made, the target instruction is put in a trace directly under the branch instruction. The trace can contain a set of such "embedded" branches.

During the formation of the trace, the instructions from a short program cycle are written without instructions that control their execution. This process is called a *loop unrolling*. If the unrolled instruction cycle does not fit into one trace, it is divided among several traces. Another way is when this cycle is rebuilt with the increased number of instructions in its core, which represent the adjacent loops, but with fewer iterations.

T-cache has several advantages:

— placing the cache RAM after the instruction decoder and storing in it a set of μops enables the processor designer to simplify the decoding stages and increases the clock frequency;

— dynamic replacement of CISC-instructions to the equivalent sequence of RISC ones or  $\mu$ ops enables the CPU to use the positive properties of RISC-instructions, i.e., to perform one instruction per clock cycle, to increase the clock frequency;

— "building in" the predicted branches in the trace minimizes the losses on the branch implementation. Now, the instructions before the branch, after branch, and branch itself can be done in a single clock cycle. In the classical processor such an instruction sequence is performed at least for three cycles;

— unrolling a cycle into a trace reduces the time spent on the branch instructions and instructions, which are tracking the cycle end;

— the instructions addressing is simplified, the associative address is provided only to the first block of the  $\mu$ ops, but not to every line of the conventional cache RAM;

— possibility of recognition and execution of the *speculative calculations*. They are the preliminary calculations, which are not performed in the operating units. For example, by the speculative calculations, the situation of zero operand addition is identified and its execution is canceled, the final value of the cycle counter can be calculated, and the respective instructions are removed from the loop.

Thus, T-cache increases the parallelism of the program just before its instructions are executed. As a result, the speedup of the program execution is increased to the extremum level.

T-cache in Pentium-4 processor consists of 6 cell blocks. One cell contains a single  $\mu$ op or an RISC-type instruction. A single block is read from the T-cache on two cycles, i.e. three  $\mu$ ops or instructions are executed per clock in this processor. The T-cache has the volume of 12K cells or 2048 blocks.

The principal feature of the T-cache is no direct relation between the instruction address and the appropriate  $\mu$ op place ( $\mu$ op or sequence of them) in the cache RAM due to the fact, that the variable length instruction of the IA-32 architecture is converted to one or more fixed-length  $\mu$ ops. Furthermore, the  $\mu$ ops are stored in the form of traces in the order of their execution. This violates the monotony of operations and continuity of the correspondence between instruction addresses and  $\mu$ op places in the cache RAM. Finally, the loop unrolling makes the traces of instruction sequences of several cycles fully violates the mutual correspondence between program instructions and  $\mu$ ops. Then, a single instruction is mapped in several  $\mu$ ops, which correspond to the different iterations of the loop or in  $\mu$ ops belonging to several traces.

The instruction address mapping mechanism into the  $\mu$ op position is needed only for those instructions, to which a jump is done. They are the first  $\mu$ ops in each trace. All other  $\mu$ ops form a chain of blocks to the end of the trace.

Both I-cache T-cache have the similarities as they are the associative memories. But they have the fundamental difference. In the classical cache RAM each memory block is associatively addressed, while in the T- cache only the first block of the trace has the associative address. The rest of the trace cells have the incremental addresses from 0 to 255 (the 0-th cell follows the 255-th cell). All blocks in a trace are connected to a bidirectional list. When some block is removed from the trace, it is "reduced", i.e. the previous block is labeled as the last one.

If the instruction, to which a jump is fulfilled, is missing in the T-cache, i.e. no trace beginning with such an address is present in it, then the instructions are read directly from the cache RAM of the second level, is decoded and executed. Simultaneously a formation of a new trace is performed, and it is loaded in the T-cache. If there is a conditional branch instruction, then the trace, starting from this instruction, is built according to the results of the branch prediction block.

The decoder processes the incoming instruction stream at a speed of not more than a single instruction per clock cycle, depending on the instruction format and presence of its prefixes. If an instruction can not be converted into a sequence of a small number of  $\mu$ ops (up to four), it is replaced by a call of a "micro-subroutine" that generates a set of  $\mu$ ops and sends them to execution.

There are some restrictions that do not allow to fill all six cells of a block by  $\mu$ ops and need to form the next block. These requirements are the placement of  $\mu$ ops which represent one instruction in one block, and limit the number of branch  $\mu$ ops, they can not be more than two.

When a branch instruction occurs in the flow, the trace building is not interrupted and is continued under the direction of the predicted branch. If the branch is estimated as done, then after the jump  $\mu$ op the  $\mu$ ops from the selected direction are placed to the trace. But the trace formation stops, when during the jump  $\mu$ op execution it becomes clear, that the branch is incorrect. And the trace is abrupted after this jump  $\mu$ op. Also, the trace forming is stopped, when the indirect branch, or subroutine call, or return instruction is found. The maximum length of the trace is equal to 64 blocks (384  $\mu$ op cells).

It may happen, that correctly predicted branch is the cycle branch. In this case, there is an opportunity to unroll the cycle. Then several iterations of it are placed in the trace to improve the speed and sampling the instructions by reducing the overheads to the branches and tracking the cycle end.

By the implementation of the next iterations of the cycle, the  $\mu$ ops are read from the T-cache till the end of the trace at the rate of one block per 2 clock cycles.

In the more superior models of the IA-64 architecture, the separate  $\mu$ op cache is used except the T-cache. But its purpose and behavior are the same, as ones of the T-cache.

#### 3.4.3 Register renaming and reorder buffer

The *register renaming* is a method to remove the data dependencies like writing after reading and writing after writing, which occur in a sequential program between the register variables. This reduces the strict conditions of the data dependencies and increases the number of instructions that can be performed simultaneously in the superscalar processor.

With this renaming, the processor does not write a result in the specified register but writes it in a special buffer, which registers have the dynamically changing addresses. For example, instead of putting the stalls after the first instruction:

MUL R1, R2, R3 ADD R2, R4, R5

the processor renames the register R2 in the second instruction, for example, to R33, and the result is written to R33, but not in R2. This resolves a dependency "write after reading" between the two instructions, and they can be performed simultaneously. In the following instructions, the dependence on data through the register R2 is restored. These instructions will read the data from R33 instead of R2.

For the first time, this method was used in 1967 at IBM 360/91 to perform the floating point operations. This computer is also known that the pipelining and dynamic instruction fetching have been introduced in it. The dynamic fetching means that the fetched instruction is not executed, but is waiting in a queue to free resources and scheduling, so to speak, it is placed on the shelf. Therefore, this method is called as an *instruction shelving*. The

mentioned queue reorders the instruction flow, therefore, it is named as a *reorder buffer*. Because of the complexity of its hardware implementation, this method was not widely used until the 90-s.

The first superscalar processors have not activated this method. It was implemented step-by-step. First, partial renaming was introduced in IBM Power, PowerPC. Then the renaming was used in all superscalar processors. The *partial renaming* applies some subset of instructions, such as floating point and the full renaming considers all the instructions.

Depending on the microarchitecture, the buffer registers are:

— part of the register memory (attached memory);

— separate register memory block;

— reorder buffer like circular buffer;

— part of the instruction shelving buffer.

Each buffer register can be 1) free, 2) *architectural register*, i.e., its address is the address in the architecture, 3) renamed register without a datum, 4) renamed register with a valid result.

Initially, the first *n* registers are the architecture registers. Then, when it becomes necessary, an additional register is selected from the available registers and it is the renamed register without a datum. After writing a result in it, it becomes a renamed register with a result. When the respective architectural register becomes free, the renamed register is assigned as the architectural one with the same address. Finally, when the architectural register is not used for a long time, it goes into a free register.

The reorder buffer and the register renaming are used in the Intel processors since Pentium–IIp. In this architecture, each executed instruction corresponds to a separate pointer to the register in a buffer. This buffer can also serve as a part of the Deferred scheduling register Renaming Instruction Shelf (DRIS). The number of registers in the buffer is a trade-off between the hardware cost and the program acceleration. In most architectures, the number of registers is in 1.5 - 8 times higher than the number of architecture registers.

The logical network, which defines the free registers, is of great complexity. Typically, it analyses a table, which maps the registers in the instruction flow and determines, which of registers are not used for a long time.

#### **3.4.4 Problems**

1) The processor has the 7-staged instruction pipeline with an instruction decoder in the second stage. Estimate the speed-up factor of the processor due to the prediction block operation if it has the probability of true predictions of 90% of branches. Consider that the program contains 25% of the branch instructions, the program is placed in cache RAM.

2) The conditions are the same as in the problem 1, but 50% of branch instructions are conditional long jumps to the instructions placed in RAM. Consider that a single cache miss lasts 100 clock cycles.

3) The conditions are the same as in problem 1, but the unpredicted branch pipeline length is equal to 30 cycles.

4) Consider a program loop, which contains 10 instructions, 3 of them provide the loop organization including a jump instruction, all the data are stored in the registers. Calculate the speed-up of the program execution if the loop is unrolled with a factor of 4. Note, that the unpredicted branch pipeline length is equal to 11 cycles, but the branch prediction is not implemented, the iteration number is a multiple of the unrolling factor.

5) The conditions are the same as in the problem 4, but the branch prediction is implemented.

6) The conditions are the same as in problem 4, but the unrolling factor is equal to maximum, and the loop before and after unrolling is placed in a

single trace of the T-cache. Note, that each instruction is of the RISC type and has the length of 4 bytes, and the maximum length of the trace is 1020 bytes.

7) Why are the reorder buffers much rarely used in the modern processors than earlier?

#### 3.5. Multithreading

### 3.5.1 Threads and multithreading

A *thread* is a major program unit that reflects the medium- or coarsegrained parallelism. It is usually relatively independent computing process, subroutine module of medium or high complexity. For a set of threads, that belong to a single program, the operational system assigns the same memory and processor resources. Within a single-processor architecture the following features of the parallel execution of threads:

— sequential execution of threads in the time slots;

- event controlled sequential execution of threads;

— parallel execution of threads.

The sequential execution of threads in the time slots is named as a *Time-Slice Multithreading*. The processor in this mode is switched between the threads at fixed time intervals. This mode uses the processor resources inefficiently, especially if several threads of different importance are pending;

The event controlled by the sequential execution of threads is named as a *Switch-on-Event Multithreading*. Such an event can be a synchronization moment of related processes. Often it is a task switching during long pauses in computations, for example, during the cache miss or file access. In this case, a process that awaits the loading data from the slow memory is suspended, freeing the CPU resources for other processes. Due to the multithreading, the delay of the access to the slow memory or other processors may be hidden from the program user. Therefore, this effect is named as a *latent time hiding*.

The disadvantage of the sequential multithreading consists in the frequent exchange of the thread context, which requires a lot of machine cycles (see interrupt handling). It also makes it difficult to exploit the parallelism of multiple operating units.

Among parallel execution flow methods, the *Simultaneous Multithreading* (SMT) is commonly used. In this case, two or more software threads run on a single processor at a time, that is, without switching between them. Then, the CPU resources are allocated dynamically according to the principle: "Do not use — give to another." This helps to utilize the CPU resources more perfectly.

The architecture IBM Power5 also applies the SMT mode. The full implementation of SMT is quite complicated. Thus, the logic networks of SMT implementation occupy 24% of the Power5 processor core. According to the IBM company, the use of SMT improves the server performance by about 35%.

# **3.5.2 Hyper-Threading**

A simplified approach of SMT is the basis of the Intel *Hyper-Threading*. technology. This technology utilizes only 5% of the crystal space for the Hyper-Threading implementation.

For the first time, the technology Hyper-Threading was implemented in the processor Intel Xeon with the Pentium-4 architecture. In one physical processor, two Logical Processors (LPs) are formed that share the CPU computing resources. The operation system and applications "see" exactly two logical CPUs, and can distribute the works between them.

One of the purposes of the Hyper-Threading is to allow a single thread to run in the virtual CPU as well as in the real CPU. For this, the processor has two basic operation modes: Single-Task (ST) and Multi-Task (MT) modes. In the ST mode, only one LP is active and uses all available resources (ST0 and ST1 modes). Another LP is stopped by the instruction HALT. When the second thread is running, then another LP is activated and CPU is put on the MT mode. The stop instruction HALT is given by the operating system.

The state or the context of each of the two LPs, called, the Architecture State (AS) is stored in a separate block. It includes the states of the registers of different types. They are general purpose, control, and interrupt service registers.

Each LP has its own Advanced Programmable Interrupt Controller (**APIC**) and a set of registers, which are supported by the Register Alias Table (**RAT**). RAT tracks the correspondence between eight general purpose registers of the IA-32 architecture and 128 physical registers of CPU, providing the register renaming.

When two threads are carrying out, two sets of counters, named Next Instruction Pointers are running. Two active LPs gain access to a shared Tcache alternately, that is, during each even cycle. While only one LP is active, it gets the exclusive access to the T-cache. Similarly, the access to the microinstruction ROM is performed. Also, the blocks that support the virtual addressing, i.e., the Instruction Translation Lookaside Buffers (ITLBs) are doubled. The instruction decoding block is shared between both software threads as well.

Five schedulers, which assign the operations to resources, process the decoded instructions regardless of their belonging to a processor LP0 or LP1 and send the instructions to the respective processing units, depending on the readiness of instructions and availability of resources.

Cache RAMs of all levels are fully shared between LPs. As a result, the most applications which have the acceleration in the multiprocessors, can be effectively computed in the Hyper-Threading mode. But there are problems. for example, if a process is situated a waiting loop, it can take all the physical resources of the CPU without letting the second LP to work. Thus, the performance can fall (to 20%), when using the Hyper-Threading mode. To minimize this effect, the Intel company recommends using the instruction PAUSE instead of empty waiting cycles.

The multi-threaded processing architectures are improved towards increasing the number of virtual processors, improved instruction dynamic fetching, increase of the operating unit workload. Thus, the Sun UltraSPARC T1 processor, which appeared in late 2006, has eight CPU cores, each of them can process up to four software threads. Therefore, the total number of parallel threads is equal to 32. The number of pipeline stages is reduced to six in it. This has simplified the branch prediction and scheduling networks and increased the processing unit loading. In 2013, the number of cores in the next architecture UltraSPARC T5 is increased to 16 and the total number of simultaneous program threads is achieved 128.

#### **3.5.3 Problems**

1) Name the conditions of the executed tasks when the time-slice multithreading is better than the switch-on-event multithreading.

2) Why is the multithreading better fitted for the coarse-grained parallelism implementation?

3) Why does the simultaneous multithreading optimize the resource balancing of CPU?

4) The Intel Xeon architecture has two thread hyper-threading, and the UltraSPARC has four thread multithreading. Explain the conditions, which determine the number of parallel threads.

5) The number of pipeline stages is usually decreased in the processors by the introduction of the multithreading in them. Explain why.

# 3.6. Memory access parallelism

# 3.6.1 Memory access consistency

Most algorithmic languages have a simple semantics of the sequential memory access. This allows the programmer to assume that all memory operations are performed in a strict order, which is defined by the program. In fact, in the today's computing system several accesses can be done to a memory at the same time, such as from the adjacent program instructions, from the DMA unit, from different program threads running in parallel. In addition, the order of the accesses, which is given by a programmer, can be exchanged both by the program compilation and by its implementation in the modern microprocessor. Therefore, it is important to consider the issues, which are related to the memory access consistency.

To analyze the memory accesses, the multiprocessor model is convenient to study. In this model, multiple Processing Units (PUs) have the parallel and independent access to the shared memory. A similar situation occurs in a single PU, which operates in a multi-threading mode.

A programmer during the programming process usually implies a model of the strictly sequential memory access or a sequential consistency model. A computer system is *sequentially consistent* if the result of any calculation in this system is the same as the calculation, which is performed by

a single processor, i.e., the calculation order is given by the program instruction sequence.

There are two requirements to the sequential consistency:

program instructions have to be executed in the same order as they do in a single processor;

— the sequential order of instructions must satisfy the unchanged order of the memory accesses.

In the consistent system, the memory is connected to PUs through a switch, which connects the memory to PUs in an order, which depends only on the compiled program. Consider the following example (Dekker's algorithm):

| PU1: F1 = 0          | PU2: F2 = 0          |

|----------------------|----------------------|

| If $F2 = 0$ then     | If $F1 = 0$ then     |

| F1 = 1               | F2 = 1               |

| {Critical procedure} | {Critical procedure} |

When PU1 is trying to start a critical procedure, it checks the flag F2 and sets its flag F1 to prevent PU2 to perform a critical procedure. The same does PU2. If the system is consistently agreed, only PU1 is the first to start a critical procedure, regardless of different circumstances. Further different consistency circumstances are considered in this example.

## 3.6.2 Sequential consistency violations

Consider some typical examples of architecture improvements that lead to the sequential consistency violations. The complexity of the consistent memory accesses depends on whether the cache RAM exists, or not.

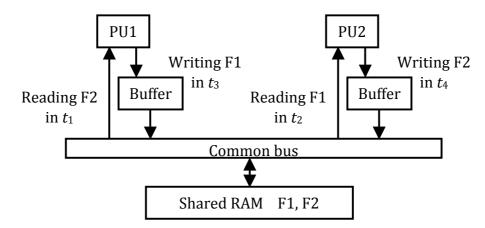

First, consider an architecture without cache RAM, but with a writing buffer. All modern processors have a writing to an intermediate buffer. The actual instruction puts a result in it, which allows completing the instruction implementation before the RAM writing transaction is completed. The system structure with two buffered PUs is shown in Fig. 3.2.

The processor may put the writing operation flag in the buffer and continue its work, not to wait for the end of the writing operation. The reading this flag is performed without buffering. The presence of buffers can disrupt the consistency. At a time, when the flag F1 = 1 writing is passed through the buffer, which is delayed by the time  $t_3$ , PU2 can read the zero flag F1 and start the critical procedure not in time.

Fig. 3.2. Violation of the memory access consistency due to the write buffers

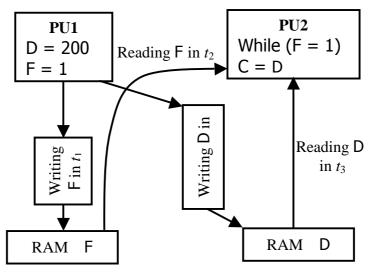

Next, consider the architecture, which has the write-reading operations of different time. The system structure in Fig. 3.3 has several memory units with different access delays.

Fig. 3.3. Violation of the sequential consistency to RAMs with different delays

The similar situation also happens if different instructions are executed in the pipeline mode with different execution time and, accordingly, different times of writing in the buffer memory. The first PU writes a new value D and sets the flag F in order to signal a second PU to read the new value. But because of various delays of accesses to both RAMs, the second PU reads actually the old value D.

# 3.6.3 Non-blocking read operations

In the consistent processor, the read operation, that follows the writing operation, is blocked until the read cell receives a new value. For the dynamic scheduling simplification, this blocking is not used. This can also lead to the consistency violation.

The examples given above showed that the processor must ensure that its previous memory access operation was finished before the next operation begins in accordance with the order of instructions in the program. This requirement is called the instruction order requirement.

#### 3.6.4 Sequential consistency in the architecture with a cache RAM

Memory caching or data duplication in the main RAM and cache RAM, which are used by several processes, is leading to situations, which are similar to those, described above. Therefore, the cache RAM systems must fulfill the same requirements of sequential consistency. The following situations are added to the situations shown above, which are related to the data duplication.

*Cache RAM coherence protocol* is a discipline of replacing the old values in the processor memory for a new one in all its copies. A new value is usually distributed by the method of invalidating or of updating of all its copies.

The cache RAM coherence is performed under the conditions:

— write operation should be recognized by all Pus, that are able to write;

— write operations in the selected memory cell must be perceived by all PUs in the same order.

However, these conditions are not enough to guarantee the memory access consistency in all conditions. To implement the cache coherency, the following methods are used.

**Detection of the writing end**. In the case, when the cache RAM is absent, the write acknowledge signal can be generated, when the written datum gets the storage. But this time is too early for a system with a cache memory.

Let each PU in Figure 3.3 has its own cache RAM. Let the operand D is stored in the cache RAM of PU2. Now, PU1 writes F after writing D in RAM, but before the moment when D comes to the cache RAM of PU2. Then, it is possible that PU2 reads a new value of F and still is reading the old value from its cache RAM, which makes the consistency violation. Therefore, PU2 should wait until D is rewritten in the cache RAM, or it is discharged before the writing to F.

That is why, the writing operation into a cell, which has a data copy in the cache RAM, requires either discharging, or overwriting confirmation signal. Moreover, all these signals must be collected together either in the shared RAM, or in PU, which initiated this writing. Only after the confirmation signal, this PU is allowed to assume, that the writing is completed.

*Write operation indivisibility*. The distribution of data exchanges to multiple cache RAMs is the operation, that takes time and can be divided into phases (not to be atomic). Therefore, the operation indivisibility condition should be obeyed.

First, the write operation in a shared cell should be completed sequentially, and for all PUs the sequence of writings should be accepted in equal order.

Secondly, it is forbidden to read a new value, until a signal is received that the old value is canceled in all cache RAM s or is overwritten there.

There are two general strategies for dealing with writes to a cache:

— *write-through*, when all data, which are written to the cache by PU, are also written to RAM at the same time;

— *write-back*, when data are written to a cache, and a *dirty bit* is set in the affected cache line. The modified line is written to RAM only when this line is replaced, otherwise, if this bit is reset then the line is discharged.

Write-through caches are simpler, and they automatically deal with the cache coherence problem, but they increase bus traffic significantly. Write-back caches are more common where higher performance is desired.

## 3.6.5 Cache RAM coherence optimizations

To increase the cache RAM speed, the coherence protocol is usually optimized. First, the independent program threads are able to make parallel and overlapped writings to cache RAM. In this situation, the written values are delayed in the writing buffer to the desired number of cycles, and the invalidating signal is sent beforehand to the cache RAMs.

Second, the read operations are delayed in accordance with the program requirements. This delay allows reading the data once again if a write confirmation signal occurs.

## **3.6.6 Consistency requirement relaxation**

As we see, the consistency requirement satisfaction, on one hand, requires extensive additional hardware costs of the parallel computing

system. On another hand, it leads to the computation slow-down even to the point where a complex computer system has a speed, which is lower than the speed of a conventional processor.

Therefore, generally, the relaxed consistency models are often used. In these models, an instruction set is divided into those that must satisfy the consistency requirements and those that may violate these requirements.

The former instructions include specialized instructions which force the hardware to follow the consistency rules. There is also a category of readmodify-write instructions, which are used for writing and reading the synchronizing flags or semaphores, such ones in Fig. 3.2. They also include special synchronizing instructions. These are instructions such as a barrier instruction, which establishes a barrier, i.e., a full stop between the number of writes and subsequent readings of the shared memory.

The weakened consistency is used for the rest of the instructions. This weakening can be on several levels depending on the computer architecture and on the weakening set. The slightest weakening is to permit reading a shared cell after writing to it. One must be conscious that, in fact, writing can really occur after reading, and this case is impossible when programming the appropriate synchronization instruction.

The further weakening is the ability to write after writing and to write or read after reading. Finally, the most relaxed weakening is permitted any violation of the memory access consistency for all instructions except the synchronization instructions.

## 3.6.7 Compiler effect

The compilers that rearrange the instructions, which access to the shared memory, may also violate the consistency, as well, as the hardware does it. Therefore, if the compiler makes the optimization, it must check

whether it provides the memory access consistency. As a result, the compilers typically perform the automatic optimization with a caution, and the effectiveness of such an optimization is very far from desirable.

On the other hand, the programmer should be aware, that because of the compiler influence, his program could lose the memory access consistency in the unpredictable circumstances.

# 3.6.8 Problems

1) Find the program solution, which prevents the consistency violation, which illustrated by Fig. 3.2.

2) CPU executes a subprogram of a large data array moving. Calculate the speed-up of this subprogram execution if the cache RAM is added, which operates in the write-back mode. Note, that the subprogram is a loop, which is executed for 10 clock cycles for moving a single 4-byte word if the data are in cache RAM and the cache hit occurs, a single access to the outer RAM adds a pipeline stall, which lasts 10 clock cycles, the cache line occupies 128 bytes.

3) The conditions are the same as in the problem 2, but cache RAM operates in the write-through mode.

4) Why is not the strict consistency model used in the real computer architectures?

5) How does the barrier synchronization work?

6) How can the compiler violate the memory access consistency?

# 4. MULTITASKING AND DATA PROTECTION

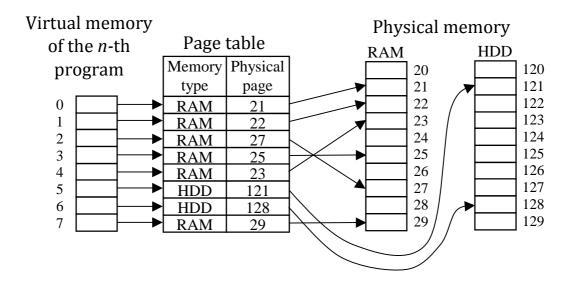

#### 4.1. Virtual memory

The principle of the virtual memory considers that the user, preparing its program, does not deal with the physical RAM but with a *virtual memory*. This memory is flat, and its capacity is equal to all the CPU address space, that is defined by the address bit width of the instruction fields and basic registers. For example, the architecture IA-32, which ancestor is the i80386 processor, can manage the virtual memory of up to 64 TB (terabytes). This is the *potential virtual memory* volume. The *real virtual memory* volume is significantly less than the potential one. It is defined by the RAM volume and by the part of the hard drive, that stands out running the virtual memory implementation.

The user has in his possession the entire address space of the computer regardless of its physical RAM volume and memory spaces for other applications in the multiprogram mode. This ensures the flexible dynamic allocation of memory and the significant convenience for the programmer. In the modern computer, all this is achieved without reducing its speed at the cost of the complications of hardware, and operating system.

At all stages of the program preparing, including its loading in RAM, the program is presented in *virtual addresses*. Only at the very execution of the machine instruction, the virtual addresses are translated into real addresses of the computer, named as the *physical* or *execution addresses*.

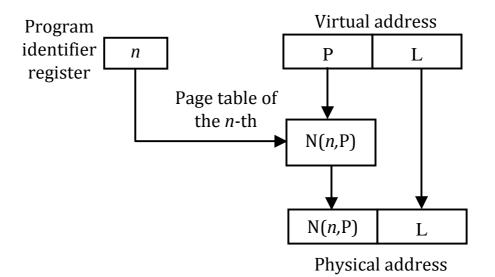

The conversion of the virtual addresses into physical ones is simplified if the physical and virtual memories are divided into identical blocks. These blocks are called *pages*. The virtual and physical memory pages are provided by numbers, called the physical and virtual page numbers, respectively.

Each physical page can store one of the several virtual pages. The byte numbering bytes both in virtual and physical pages is the same. The program during its loading can be placed to any available physical pages, regardless of whether they are consecutive or not. Memory paging enables more efficient carrying out the information exchange between the external memory and RAM, as the program page should not be loaded until it is needed.

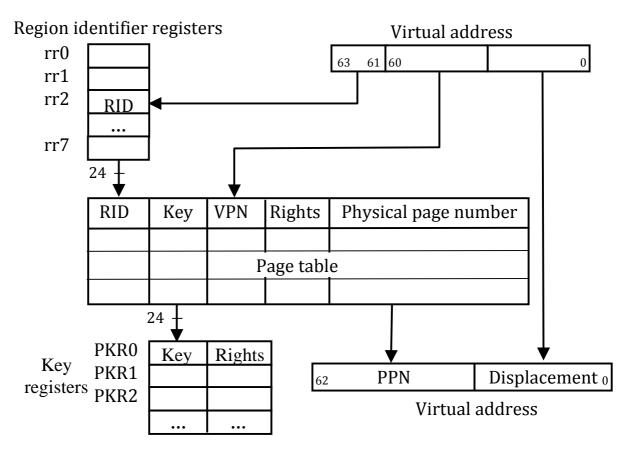

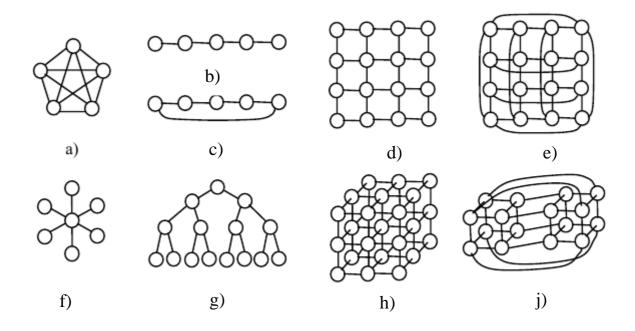

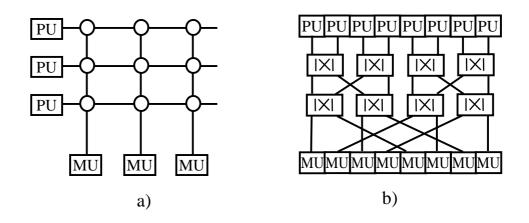

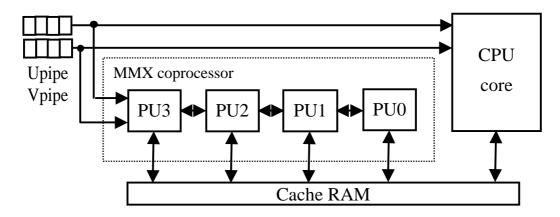

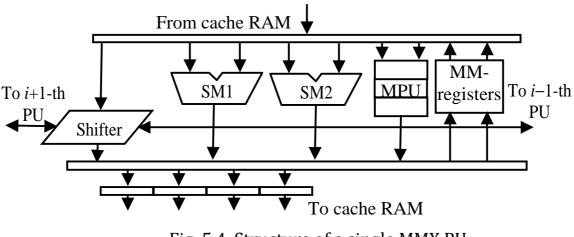

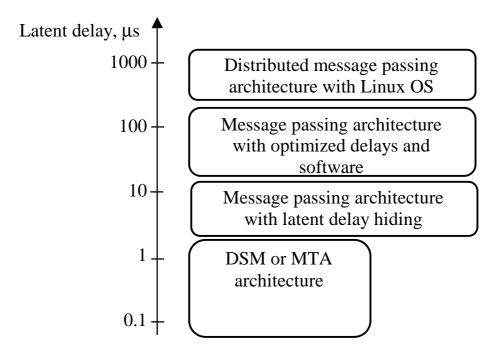

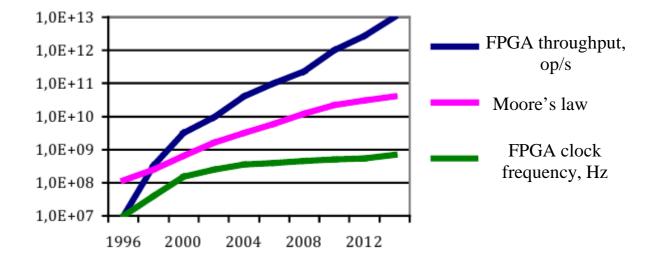

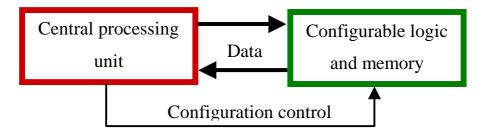

Initially, the initial program page is loaded and gets the control. If in the runtime the another page has to be loaded, then the automatic operation system call is done, that organizes the load of this page. This page before its loading usually forces a process, when the unneeded program page frees the space by moving itself to the external memory. Such a page replacement is called as a *page swapping*. The respective part of HDD, where the virtual memory is allocated, and where the swapped pages are stored is named as a *swap file*. The size of this file depends on the hard disk volume and the operating system type and can be defined by the computer system administrator.