Sergiyenko A.M., Korneychuk V.I.

# Digital Networks Design

#### УДК 681.3 ББК 32.973-01 С 34

Рецензенти: В.П. Тарасенко, доктор технічних наук, професор, завідуючий кафедрою спеціалізованих компьютерних систем НТУУ "КПІ"; О.В.Бузовський, доктор технічних наук, професор, кафедра обчислювальної техніки НТУУ "КПІ".

#### С34 Сергієнко А.М., Корнійчук В.І.

#### Digital Networks Design (Компьютерна схемотехніка). – К.: «Корнійчук», 2007. – 80 с.

#### ISBN 966-7599-41-8

Розглянуті способи побудови типових вузлів, блоків та пристроїв компьютерів від найпростіших логічних схем до ядра мікропроцесора. Приведено опис типових вузлів на мові VHDL. Для студентів, аспірантів, викладачів вузів з викладанням на англійській мові, а також для читання спеціалістами в галузі електроніки, вимірювальної і обчислювальної техніки та зв"язку.

ББК 32.973-01

#### C34 Sergiyenko A.M., Korneychuk V.I. Digital Networks Design – К.: «Корнійчук», 2007. –80 р. ISBN 966-7599-41-8

Methods of design of base modules and devices for computers are considered, beginning at simplest logic networks and finishing at microprocessor cores. The base modules are described by the VHDL language. For the students, aspirants, high scool lecturers, as well as for reading by the specialists at the fields of electronic engineering, measurements, communications and computer engineering.

#### ББК 32.973-01

ISBN 966-7599-41-8

© Сергиенко А.М., Корнейчук В.И., 2007

Sergiyenko A.M., Korneychuk V.I.

## Digital Networks Design

Сергієнко А.М., Корнійчук В.І.Компьютерна схемотехніка (на англійській мові)

> Київ 2007

##

| <ul> <li>Leader advantation</li> </ul>          | 2  |

|-------------------------------------------------|----|

| 1. Logic network basics                         | 3  |

| 1. Integral circuits                            | 3  |

| 2. Boolean algebra                              | 7  |

| 3. Combinational logic networks                 | 11 |

| 4. Triggers                                     | 14 |

| 5. Decoders                                     | 17 |

| 6. Multiplexers                                 | 19 |

| 7. Encoders                                     | 20 |

| 8. Shifters                                     | 21 |

| 9. Binary adders                                | 21 |

| 10. Registers                                   | 23 |

| 11. Counters                                    | 25 |

| 12. Programmable logic devices                  | 27 |

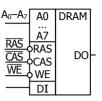

| 2. Memory units                                 | 34 |

| 1. General properties                           | 34 |

| 2. Fast memory units                            | 35 |

| 3. Register file                                | 36 |

| 4. Stack memory                                 | 37 |

| 5. Cache memory                                 | 37 |

| 6. Memory integral circuits                     | 39 |

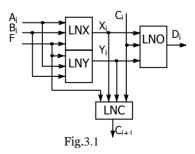

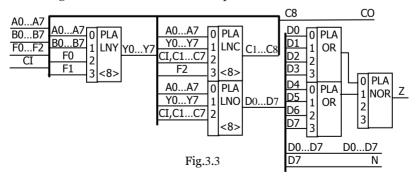

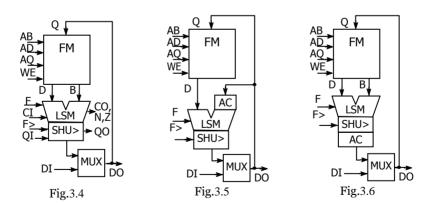

| 3. Networks for arithmetic and logic operations | 43 |

| 1. Arithmetic and logic units                   | 43 |

| 2. Datapath                                     | 45 |

| 3. Binary multipliers                           | 47 |

| 4. Binary dividers                              | 50 |

| 5. Hardware pipelining                          | 51 |

| 4. Control networks                             | 53 |

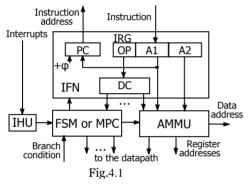

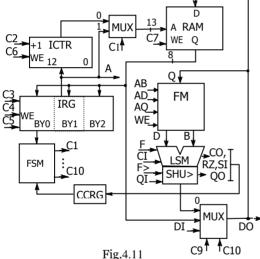

| 1. CPU control unit                             | 53 |

| 2. CPU instruction set                          | 54 |

| 3. Control unit structure                       | 55 |

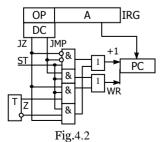

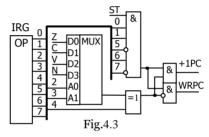

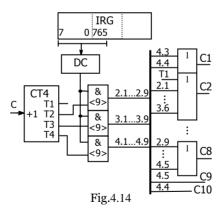

| 4. Instruction fetch networks                   | 56 |

| 5. Finite state machines                        | 58 |

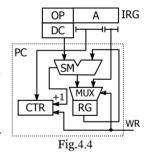

| 6. Microprogram controllers                     | 62 |

| 7. Example of CPU design                        | 64 |

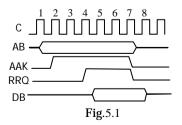

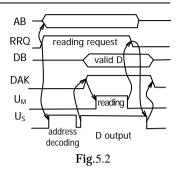

| 5. Interfaces                                   | 69 |

| 1 Common busses                                 | 69 |

| 2 AMBA interface in SOC design                  | 71 |

| List of abbreviations                           | 78 |

| Bibliography                                    | 79 |

|                                                 | 1) |

### 1. Logic network basics

#### **1.1 Integral circuits**

Integral circuits (ICs) form the basis both of the electronic industry and of all its product applications. The transistor is the atom element of ICs. A single two input logic element (LE), named a **logic gate**, can be formed by three or four **complementary metal-oxide-semiconductor** (CMOS) transistors. The digital IC volume is usually measured by the number of equivalent two input logic gates. Due to this number, all the ICs are divided to small scale integration ICs and to **large scale integration** (LSI) ICs. The small scale integration circuits have the volume of up to hundreds of gates. The standard logic ICs, **programmable logic arrays** (PLAs) and different buffer ICs belong to these circuits.

A set of LSI circuits consists of microprocessors, microcontrollers, memory ICs, **application specific integral circuits** (ASICs), and **application specific standard products** (ASSPs). The modern LSI circuits can contain up to tenths millions of gates. Besides, memory ICs have the volume of up to billions of bits.

In the seventies, the most popular logic ICs were circuits of the series SN74, which consisted of up to thousand of different transistor-transistor logic (TTL) circuits. In USSR the analogous ICs were circuits of the series K155. Some analogous representatives of this series are widely used now, but they are implemented by the modern CMOS transistor technology. In most cases, these ICs are buffers, registered buffers, multiplexers, invertors, simplest logic networks (LNs).

PLAs were designed at the end of seventies on the base of the **read only memory** (ROM) technology. The PLA consists of a set of logic cells. Each of them is a multi-input logic element with a trigger on its output. The PLA programming means the forming bridges between the data sources and the logic element inputs. In PLAs the metal-nitrogenium-oxid-semiconductor (MNOS) transistors play the role of bridges, and they are programmed as the similar bridges in the flash memory. Usually the number of logic cells and the data source number do not exceed ten and fifty, respectively. Now PLAs are widely used as, so called, glue logic circuits, because they "glue" the LSI circuits together in the system.

The **microprocessor** is the main operational unit of the computer. Its functionality is undefined not only by its production but also during its use. It depends on user programs and operational systems. The **microcontroller** has the similar properties as the microprocessor has, but its functionality is usually fixed strictly in the user device where it is built in. This means that it performs a single program, which is usually not exchanged during all its living time. The **digital signal processing** (DSP) processors form a separate subset of microcontrollers. Microprocessors are described in the 4-th chapter of this book.

The memory ICs are divided into **random access memories** (RAMs) and ROMs. These ICs are described in the 2-nd chapter.

ASIC has its name because of its functionality which is fixed during the design and manufacturing processes. Therefore, ASIC implements a single but complex function. ASIC examples are modem circuits, hard disc controllers, parts of the computer chipset. Because of the increase of circuit design cost, the ASIC manufacturing is worth of the profit when their stocks have more than million of chips.

ASSPs form a wide set of different devices. Their functionality is less than one of microcontrollers but it is enough to be adapted to a set of different applications. They are application specific memory ICs, like graphic adapter RAM, flash ROM. The microcontrollers with the specific set of peripheral units, for example, MP3 player, MPEG encoder, belong to the ASSP set as well. The system which contains microprocessor, application specific processors, memory units, peripheral units, etc., coupled in a single chip, is named as the **system-on-the-chip** (SOC). From the designer point of view, the ASSP is an ASIC which is developed to satisfy the adaptation possibilities. **Complex programmable logic devices** (CPLDs) and **field programmable gate arrays** (FPGAs) form the specific subsets of ASSPs.

The CPLD structure consists of up to tenths of PLAs placed in a single chip, and connected through a programmable switch array. Its logic volume is usually less than ten thousands of equivalent gates (i.e. two input logic elements).

The FPGA was invented in eighties as the alternative to the CPLD. The FPGA represents the array of 2-6 input logic elements, triggers (registers), and wire parts, which are connected together by a set of bridges. These bridges are formed by the field effect transistors (FETs), controlled by the special programming triggers. The routes of the FPGA netlist are programmed by the exchange of the electric field in the FET gates, and this is the root of the FPGA name. Before the FPGA operation, the programming bit stream, named **configuration**, is automatically loaded into FPGA from the outer ROM. This process is named as FPGA configuring. Modern FPGAs contain RAM units, hardware multipliers, fast speed interfaces, microprocessor cores and other units. Their logic volume reaches ten millions of equivalent gates. Sometimes FPGA is a part of another complex ASSP.

The CPLD and FPGA project designing is cost effective and has the small design period. Therefore, it is the alternative to ASIC when the series of production of the specific device does not succeed hundred thousands of units. As a result, the number of new FPGA and CPLD projects increases, and the number of ASIC projects decreases every year.

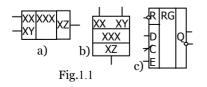

Due to the standards, accepted by countries of former USSR, ICs and their parts are drawn in the schematic diagrams as rectangles, named the **network symbols**. This symbol has three fields as is shown in Fig.1.1 (a). The left field signs the input marks (xx, xy), the right field signs the marks of outputs (xz), and the IC function name is placed in the middle (xxx). In the symbol of the simple IC the left and/or right field can be absent. Due to standards of western countries, the symbol fields are not separated by lines, and additional input-output fields can be placed in upper and bottom sides of the symbol.

If the IC pin serves both as input and as output, then its name can be placed in the left or right field. In such situation the symbol <> (bidirectional) is attached to this name. When it is needed, the IC symbol can be rotated clockwise to 90° (Fig.1.1 (b)). Some name characters have the common meaning for many ICs, and they are described in the Table 1.1. Fig.1.1(c) illustrates the register with inverse reset input, direct and inverse output, and loading by the rising edge of the clock signal when the enable signal is high.

| Ta | able 1.1      |

|----|---------------|

| Α  | - address bus |

| Α                   | - address bus                         | G       | - generator                               |  |  |  |

|---------------------|---------------------------------------|---------|-------------------------------------------|--|--|--|

| ALU                 | - arithmetic-logic unit               | MUX     | - multiplexor                             |  |  |  |

| В                   | - unidirectional or bidirectional bus | MPU     | - multiplier unit                         |  |  |  |

| С                   | - clock input                         | Mn      | - modulo n arithmetic unit                |  |  |  |

| CI,CO               | - carry input, carry output           | Q       | - data output, can be bidirectional       |  |  |  |

| CD                  | - coder                               | Q, nQ   | - negated data output                     |  |  |  |

| CPU                 | - central processing unit             | R R     | - reset input                             |  |  |  |

|                     | - counter, counter modulo n           | RG      | - register                                |  |  |  |

| D                   | - data input, can be bidirectional    | S       | - set input                               |  |  |  |

| DC                  | - decoder                             | SHU     | - shifter unit                            |  |  |  |

| E                   | - enable input                        | SM      | - summator, adder, subtractor             |  |  |  |

| F                   | - control input, for function coding  | Т       | - latch, 1-bit latch register             |  |  |  |

| GND                 | - signal of the logic '0' (ground)    | TT      | - trigger, flip-flop, 1-bit register      |  |  |  |

| 0                   | - negated input or output (see        | X/Y     | - logic network, transfers X to Y         |  |  |  |

|                     | Fig.1.1(c))                           |         | 0                                         |  |  |  |

| /, ⊳                | - rising edge clock input             | 1       | - repeater, OR function                   |  |  |  |

| // *                |                                       |         | (Fig.1.3(a))                              |  |  |  |

| ∖∕⊲                 | - falling edge clock input            | &       | - AND function (Fig.1.3(c))               |  |  |  |

| $\overline{\Delta}$ | - mark of open emitter (drain)        | ==      | - equality function                       |  |  |  |

|                     | output                                |         |                                           |  |  |  |

| $\wedge$            | - mark of open collector (source)     | -1 A    | - Exclusive OR function                   |  |  |  |

| $\Diamond$          | output                                | -1,⊕    | <ul> <li>Exclusive OR function</li> </ul> |  |  |  |

| $\Diamond$          | - tristate output                     | #       | - digital function                        |  |  |  |

| -                   | 1                                     |         | 0                                         |  |  |  |

| $\times$            | - not logical input or output         | <n></n> | - mark of the grouped component           |  |  |  |

|                     |                                       |         | (component is repeated <i>n</i> times)    |  |  |  |

**Logic elements** (LEs) form a **component basis** of ICs, which is proper to the given IC technology. The IC is designed on the base of the component library, which is formed by the LEs of different kinds, with different input number, delay t, power consumption and space on the chip surface. The quality, consumer properties of ICs depend on its technology, component basis, delay t, maximum clock period  $t_c$ , supply voltage V, power consumption P, logic level voltages  $L_0$  and  $L_1$ , its output buffer loading characteristics, and others parameters.

In the logic electric circuits bits a 0 and a 1 are represented by two **logic voltage levels**  $V_0$  and  $V_1$ . Sometimes they are represented by low and high current level, or positive and negative current. In any case, the low level is marked as L, and high level – as H. When  $V_0 = L$  and  $V_1 = H$  the IC is named as one with the **positive logic**, and when  $V_0 = H$  and  $V_1 = L$  then it is the **negative logic** IC. Below we will consider the positive logic ICs. The working voltage range (usually from 0 to *V*) is divided into three ranges: *V*-H<sub>t</sub>, L<sub>t</sub>-0, and H<sub>t</sub>-L<sub>t</sub>, which are illustrated by Fig.1.2. If the signal magnitude is in the range *V*-H<sub>t</sub> (L<sub>t</sub>-0) then LE

accepts this signal as the bit 1 (0). And if the signal magnitude stays in the threshold  $H_t-L_t$  then LE can recognize it both as 0 and as 1, and LE operates unstable. Therefore, such signal magnitude is allowed only in the moment of LE switching.

Some buffer circuits have the operation mode in which their outputs have the high impedance. Then the signal on their outputs is allowed to be in the threshold  $H_t$ - $L_t$  for a long time, because this operation is provided to build common busses. For this reason the state, when signal is in range  $H_t$ - $L_t$ , is named as **third state** (Z-state), and these buffers and busses are named as **tristate** ones.

Modern ICs often have two or more **supply voltages**. One of them is usually equal to V=3,3 volts, and is used for feeding the input and output buffers. Another voltages are much less (down to

*V*=1 volt), and are used to supply the inner circuits. Thus, inner and outer voltage logic levels are different ones. The outer voltage logic levels in most of cases obey the standard TTL logic levels, i.e. level  $H_t$  is 2,4 volts, and level  $L_t$  is 0,8 volts.

The IC speed is derived from the **propagation delays** *t* of its LEs and other components. In general, these delays depend on the route of the signal propagation, and on the capacitance at the LE outputs. This capacitance in CMOS circuits is proportional to the number of LE inputs, which are attached to this LE output. This number is named as the LE **fanout**.

Sometimes the delay  $t^{0.1}$  of propagation of transition from L to H is different from the delay  $t^{1.0}$  for transition from H to L. As a rule, these delays are shorter than propagation delay of generating the transition from Z to H or from Z to L and visa versa at the LE output (see the **waveform**  $V_Z$  in Fig.1.2). Besides, all the delays become shorter with temperature and power voltage increase. As a result, each LE has the delay function which depends on the fanout, transition form, voltage and temperature. In the **computer-aided design** (CAD)-tools the LE libraries usually contain such delay functions, which are taken into account during the logic synthesis. In the modern ICs, the propagation delays in wires can be higher then delays of LE switching. Therefore, by the design of such ICs the capacitance and inductance of the wires, which cause the delay, are taken into account as well. In simple calculations the LE delay can be considered as that that is equal to a constant for all the similar LEs, and is equal to the maximum delay over all possible delays.

The **power consumption** of modern ICs is caused, in general, by the switching processes in them. Some power consumption is forced by the current leakage, but it is much less for CMOS circuits. The **switching** is the effect of charging and discharging of the LE capacitances, and it can be estimated by the formula:

$$P = C_{\rm L} V^2 E_{\rm S} f_{\rm C} / 2, \qquad (1)$$

where  $C_L$  is the physical capacitance at the LE output,  $E_S$  is the average number of output transitions per clock cycle (the switching activity, it is typically 20% in most designs), and  $f_C$  is the clock frequency. Due to the formula (1), reduction of any of its factors will result in a lower power consumption of the IC. The reduction of the supply voltage V is the most attractive, because it is in a quadratic relation to power. But this has a negative impact on the speed of the design because the voltage reduction increases the delay t of LEs.  $C_L$  is the LE loading, which is proportional to LE fanout and wire lengths.  $C_L$  decreasing is more effective because it decreases the LE delay, and thus increases the design throughput.  $f_C$  is derived from the maximum delay in the chains of LEs which route the logic signals from the source trigger to the destination trigger, and therefore, it increases by the minimizing such chains.

The IC design strategy is directed to minimize the LE number, its fanout, its input number, and its number in logic chains, considering the given component library. Therefore, the IC logic synthesis is complex task with respect to a set of contradiction goals like hardware and power minimization, and speed maximization. This task is implemented now automatically in many modern CAD-systems. But to achieve success, the designer has to know excellently the rules and laws of the logic synthesis to be able to direct this process. Moreover, often the excellent IC projects are designed by hand, because the automatic results occur to be bad. In the following chapters we will look into the logic design processes.

#### 1.2 Boolean algebra

The LE is the circuit which operation can be described by the simple combinational logic function or the **Boolean function** (BF). This function can have only two meanings, or significances: 0 and 1 or *false* and *true*. The BF arguments also have only two such meanings.

The simplest BF Y=f(X) is given by its significances by X=0 and X=1. In general, there are four such functions, which are given in the **truth Table** 1.2. BFs  $f_0$  and  $f_3$  are constants 0 and

1. Significances of  $f_1$  are equal to X, therefore LE which implements  $f_1$  is named as **buffer**. Its graphical symbol is illustrated by Fig.1.3 (a). Here in the left side is the symbol due to former Soviet Union countries standards, or to IEEE standard. In the right side is the symbol, which is adopted in western countries. BF  $f_2$  exchanges 0 to 1, and 1 to 0. Such transform is named as **inversion**, marked as  $\overline{X}$ , and spelled as not X. LE which implements  $\overline{X}$  is named as an **invertor**, or a NOT gate (see Fig.1.3 (b)). To define the two argument BF  $f(X_1, X_2)$  one has to give its significances on four argument sets  $(X_1, X_2)$ , which is illustrated by the Table 1.3. Such a task can be implemented by one of 16 ways. And 16 different

| Table | 1.2. |

|-------|------|

|       |      |

|   | X | $f_0$ | $f_1$ | $f_2$ | $f_3$ |

|---|---|-------|-------|-------|-------|

| Γ | 0 | 0     | 0     | 1     | 1     |

| Γ | 1 | 0     | 1     | 0     | 1     |

| Tab     | le 1.3 |                 |                |    |

|---------|--------|-----------------|----------------|----|

| $X_1$ , | $X_2$  | $X_1 \cdot X_2$ | $X_1 \lor X_2$ | =1 |

| 0       | 0      | 0               | 0              | 0  |

| 0       | 1      | 0               | 1              | 1  |

| 1       | 0      | 0               | 1              | 1  |

| 1       | 1      | 1               | 1              | 0  |

BFs can be distinguished. But practically, the following six BFs are used:  $X_1 \cdot X_2$  (AND function, or **conjunction** or '&'),  $X_1 \lor X_2$  (OR, **disjunction**, or '1'), **Exclusive OR** (shortly EXOR, or '=1'), and their negations:  $\overline{X_1 \cdot X_2}$  (Not AND, shortly NAND),  $\overline{X_1 \lor X_2}$  (Not OR, shortly NOR) and Exclusive Not OR (shortly XNOR, or '==' that means equality). LEs or gates, which implement these BFs, have the proper names (see Fig.1.3(c-h)).

In most of cases of analysis or synthesis of logic networks the functions AND, OR, and NOT are used. These functions form, so called, **Boolean algebra**. Besides, AND, OR functions can have large number of arguments. From the Table 1.3, one can derive the following Boolean algebra equalities and identities:

$$\begin{split} X & \lor 0 = X, \qquad X \lor 1 = 1, \qquad X \lor X = X, \\ X \cdot 0 = 0, \qquad X \cdot 1 = X, \qquad X \cdot X = X, \\ X \lor Y = Y \lor X, \qquad X \cdot Y = Y \cdot X, \qquad (2) \\ (X \lor Y) \lor Z = X \lor (Y \lor Z), \qquad (X \cdot Y) \cdot Z = X \cdot (Y \cdot Z), \\ X \lor \overline{X} \cdot Y = X \lor Y, \qquad X \cdot \overline{Y} \lor X \cdot Y = X, \\ X \cdot (Y \lor Z) = (X \cdot Y) \lor (X \cdot Z), \qquad \overline{X} \lor \overline{Y} = \overline{X} \cdot \overline{Y}, \\ X = \overline{\overline{X}}, \qquad X \lor \overline{X} = 1, \qquad X \cdot \overline{X} = 0, \qquad \overline{0} = 1, \quad \overline{1} = 0, \\ \overline{X \cdot Y} = \overline{X} \lor \overline{Y}, \qquad X \lor Y = \overline{\overline{X} \cdot \overline{Y}}. \end{split}$$

Here and below the higher priority of AND (point) operation is considered.

The number of different BFs is derived from

the argument number n, and is equal to  $2^{2^n}$ , where  $2^n$  is the number of different argument sets. When n=3 we can get 256 BFs. But it is not necessary to build a set of 256 LEs to select from it the needed function of 3 arguments. It is enough to have a set of gates of AND, OR, NOT-type. The fact is that any BF is represented by the superposition of these functions using the following equation, named as a **sum-of-product form**:

$$f(X_1, X_2, ..., X_n) = V f(\alpha_1, \alpha_2, ..., \alpha_n) \cdot X_1^{\alpha_1} \cdot X_2^{\alpha_2} \dots X_n^{\alpha_n},$$

(3)

where the OR function is given on all the sets  $(\alpha_1, \alpha_2, ..., \alpha_n)$ , and

$$X_{i}^{\alpha_{i}} = \begin{cases} X_{i}, \text{ when } \alpha = 1; \\ \overline{X_{i}}, \text{ when } \alpha = 0; \end{cases} \quad i=(1,...,n).$$

$$X^{\alpha} = \begin{cases} 1 \text{ when } X = \alpha; \\ 0 \text{ when } X \neq \alpha. \end{cases}$$

Really,

As a result, the function, named the term, is equal to  $X_1^{\alpha_1} \cdot X_2^{\alpha_2} \dots X_n^{\alpha_n} = 1$  only if  $X_i = \alpha_i$  for all values of *i*. And in this situation

$$f(\alpha_1, \alpha_2, ..., \alpha_n) = 0 \lor 0 ... f(\alpha_1, \alpha_2, ..., \alpha_n) \cdot 1 \lor 0 ... 0 \lor 0,$$

i.e. the left part of the equation (3) is equal to the right one.

Consider an example. There are three lighting switches in the room. The goal is to design the logic network which provides switching on and off by a single switch not to touch the other switches. Consider one state of the switch is zero (0), and another one is one (1). Because there are three switches, the network must implement the logic function of three arguments. Let lighting is off when all the switches are in the state 0, i.e. the switch state is 000. Then a single exchange of any switch forces lighting on. Therefore, BF has to be equal to 1 on the set of states 001, 010, and 100. Any exchange of these states

| Table 1.4 |       |       |   |  |  |  |  |

|-----------|-------|-------|---|--|--|--|--|

| $X_1$     | $X_2$ | $X_3$ | f |  |  |  |  |

| 0         | 0     | 0     | 0 |  |  |  |  |

| 0         | 0     | 1     | 1 |  |  |  |  |

| 0         | 1     | 0     | 1 |  |  |  |  |

| 0         | 1     | 1     | 0 |  |  |  |  |

| 1         | 0     | 0     | 1 |  |  |  |  |

| 1         | 0     | 1     | 0 |  |  |  |  |

| 1         | 1     | 0     | 0 |  |  |  |  |

| 1         | 1     | 1     | 1 |  |  |  |  |

forces lighting off. Finally, when switches are in the states 011, 101, 110 then BF has to be a 0, i.e. the light is off. The next exchange of any switch makes lighting on, which gives f(1,1,1)=1. The meanings of the BF *f* are shown in the Table 1.4.

Then we represent the derived BF in the form (3):

$$\begin{split} f(X_1, X_2, X_3) &= f(0, 0, 0) \cdot X_1^0 X_2^0 X_3^0 \lor f(0, 0, 1) \cdot X_1^0 X_2^0 X_3^1 \lor f(0, 1, 0) \cdot X_1^0 X_2^1 X_3^0 \lor f(0, 1, 1) \cdot X_1^0 X_2^1 X_3^1 \lor \\ & \lor f(1, 0, 0) \cdot X_1^1 X_2^0 X_3^0 \lor f(1, 0, 1) \cdot X_1^1 X_2^0 X_3^1 \lor f(0, 0, 0) \cdot X_1^0 X_2^0 X_3^0 \lor f(1, 1, 1) \cdot X_1^1 X_2^1 X_3^1 = \\ &= 0 \cdot \overline{X}_1 \cdot \overline{X}_2 \cdot \overline{X}_3 \lor 1 \cdot \overline{X}_1 \cdot \overline{X}_2 \cdot X_3 \lor 1 \cdot \overline{X}_1 \cdot \overline{X}_2 \cdot \overline{X}_3 \lor 0 \cdot \overline{X}_1 \cdot X_2 \cdot \overline{X}_3 \lor 0 \cdot X_1 \cdot \overline{X}_2 \cdot \overline{X}_3 \lor 0 \cdot \overline{X}_1 \cdot \overline{X}_2 \cdot \overline{X}_3 \lor 0 \cdot \overline{X$$

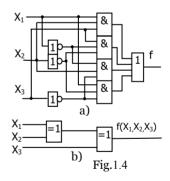

The network, which implements this BF, is shown in Fig.1.4 (a). It consists of three NOT gates for negating the input signals, four AND gates, and a single OR gate. This network can be simplified by the use of the Exclusive OR gates. The analysis of the Table 1.4 shows that this BF is the sum modulo 2 of input variables. Therefore, this function can be implemented by two 2-input gates, as it is shown in Fig.1.4 (b).

The sum-of-product form (3), named as AND/OR form, is not unique method of deriving BFs. Really, using the relations  $X = \overline{\overline{X}}$ , and  $\overline{X \lor Y} = \overline{X} \cdot \overline{Y}$  for the previous example, we can get the following forms

| $f(X_1, X_2, X_3) = \overline{\overline{X}_1 \overline{X}_2 X_3 \cdot \overline{X}_1 X_2 \overline{X}_3 \cdot X_1 \overline{X}_2 \overline{X}_3 \cdot X_1 X_2 X_3} =$                                                                   | (AND-NOT/AND-NOT)                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| $=\overline{\overline{X_1 \vee X_2 \vee \overline{X_3}}} \cdot \overline{X_1 \vee \overline{X_2} \vee X_3} \cdot \overline{\overline{X_1} \vee X_2 \vee X_3} \cdot \overline{\overline{X_1} \vee \overline{X_2} \vee \overline{X_3}} =$ | = (OR/AND-NOT) (4)                          |

| $=\overline{X_1 \vee X_2 \vee \overline{X}_3} \vee \overline{X_1 \vee \overline{X}_2 \vee X_3} \vee \overline{\overline{X}_1 \vee X_2 \vee X_3} \vee \overline{\overline{X}_1 \vee \overline{X}_2 \vee \overline{X}_3}$                 | $\overline{\overline{X}_{3}}$ . (OR-NOT/OR) |

Both the function and its inversion can be represented by the form AND/OR. This gives another four forms:

$$f(X_{1}, X_{2}, X_{3}) = \overline{\overline{X}_{1} \overline{X}_{2} \overline{X}_{3}} \vee \overline{\overline{X}_{1} X_{2} X_{3}} \vee \overline{X_{1} \overline{X}_{2} X_{3}} \vee \overline{X_{1} X_{2} \overline{X}_{3}} =$$

(AND/OR-NOT)

$$= \overline{\overline{X}_{1} \overline{X}_{2} \overline{X}_{3}} \cdot \overline{\overline{X}_{1} X_{2} X_{3}} \cdot \overline{X_{1} \overline{X}_{2} X_{3}} \cdot \overline{X_{1} X_{2} \overline{X}_{3}} =$$

(AND-NOT/AND)

$$= (X_{1} \vee X_{2} \vee X_{3}) \cdot (X_{1} \vee \overline{X}_{2} \vee \overline{X}_{3}) \cdot (\overline{X}_{1} \vee X_{2} \vee \overline{X}_{3}) \cdot (\overline{X}_{1} \vee \overline{X}_{2} \vee X_{3}) =$$

(OR/AND) (5)

$$= \overline{\overline{X_{1} \vee X_{2} \vee X_{3}}} \cdot \overline{X_{1} \vee \overline{X}_{2} \vee \overline{X}_{3}} \cdot \overline{\overline{X}_{1} \vee X_{2} \vee \overline{X}_{3}} \cdot \overline{\overline{X}_{1} \vee \overline{X}_{2} \vee X_{3}}.$$

(OR-NOT/OR-NOT)

Each of the relations (3), (4), (5) is called as the **normal form** of the BF representation. They can be useful by designing of LNs, based on the concrete gate library.

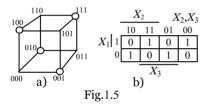

Many transformations of BF can be usefully interpreted when BF is graphically represented. In the geometrical sense a set  $(X_1^{\alpha_1}, X_2^{\alpha_2}, ..., X_n^{\alpha_n})$  can be represented by the vector, which forms a point in the *n*-dimensional space. All 2<sup>n</sup> combinations of vectors form the nodes of the *n*-dimensional cube. Marking the nodes, where BF is equal to 1, we derive the graphical representation of BF. These marked nodes represent the terms of the equation (3). In Fig.1.5 (a) the 3-

dimensional cube of the function (4) is drawn. The number of variables  $X_i$ , which exchange its coordinate when traversing from one node to another one, is named as the distance between these nodes. Looking at Fig.1.5, one can to prove that the distance between all couples of the nodes is equal to 2. A single node of the *n*-dimen-

sional cube, which BF is equal to one, is named as a 0-**cube**. Two 0-cubes, which are connected by an edge, form the 1-cube. This means that in the 1-cube the distance between two nodes is equal to a 1, and two respective terms are different in a single variable. Four nodes, which form the square plane, belong to the 2-cube, and visa versa. Often the cubes are named as **prime implicants**, because they represent the OR function of terms (implication), which can be reduced.

BFs are often represented graphically by **Karnaugh maps** (KM) or **Veitch diagrams** (VD). KM is built by unfolding the *n*-dimensional cube to the plane. The cube nodes are represented by squares of the KM, which coordinates are equal to the coordinates of the cube nodes. To simplify the representation, the rows and columns of KM, where the coordinate is equal to 1, are marked by the bold line. KM of BF (4) is shown in Fig.1.5 (b). Due to the fact, that selecting the *k*-cubes minimizes BF, and these cubes are easily found in KM, KM is often used in the LN synthesis. Such a process is shown below.

#### 1.3 Combinational logic networks

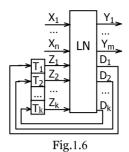

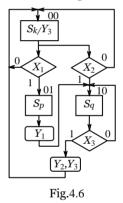

The operation algorithm for any **digital network** with *n* inputs and *m* outputs can be described by *m* Boolean equations  $Y_i = f_i(X_1, X_2, ..., X_n, Z_1, Z_2, ..., Z_k)$ , (i=1,...,m), where  $Y_i, X_j$  are output and input variables (j=1,...,n),  $Z_t$  are variables which represent the inner state of the network (j=1,...,n). This is the state of some

memory elements, which usually are triggers. Such a network can be represented by two parts (see Fig.1.6). One of them consists of triggers (T). Another one contains LEs, which are connected into the **combinational logic network** (LN). Both parts interact through variables  $Z_t$ , which characterize the trigger states, and variables  $D_i$ , which are the trigger **stimulating functions**.

The main feature of LN consists in the following. When all the transition processes are finished in the inner LEs, then the output signals depend only on the input signals, and the inner signal states are not needed to

derive these output signals. Therefore, equivalent LNs can have different inner structure. The goal of the logic synthesis is to minimize the LN complexity, and maximize its speed, selecting its optimum inner structure.

To develop LN, based on the given LE library, BF has to be represented by the superposition of LE functions. These LE functions are named as **operators**, and their superposition is the **operator representation** of BF. Such representation process is named as the mapping of BF into LN. As the base BF for the logic synthesis, the minimum normal form is selected. The **minimum normal form** is one of eight BFs (3), (4), (5), which has the minimum number of input signal symbols and their negations.

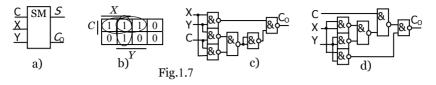

Consider the example of the logic synthesis of the carry network of an adder (Fig.1.7 (a)). The carry function C<sub>0</sub> is equal to a 1 if two or more arguments are equal to a 1. KM of this BF is shown in Fig.1.7 (b).

The 1-cube of *n* variables, which was mentioned in the previous chapter, has the property, that it can be represented by the AND function of *n*-1 variables. Three 1-cubes are selected in the KM in Fig.1.7 (b). One of them is  $((C,X,Y),(C,X,\overline{Y}))$ . Due to the fact that the distance between terms in the cube is equal to one, the conjunction of them is  $CXY \lor CX\overline{Y} = CX(Y \lor \overline{Y}) = CX \cdot 1 = CX$ . As a result, the "gluing" of terms occurs, and BF is reduced.

By BF minimizing, its KM is fully covered by 0-,1-,...*k*- cubes, as it is shown in Fig.1.7 (b). The conjunctions of terms, representing those (prime implicants) are reduced as shown above. The resulting BF is the conjunction of all reduced prime implicants. In our example it is  $C_0 = CX \lor CY \lor XY$ . This is the first minimum normal form. Another 7 minimum normal forms can be derived as in (4), (5):

$$\begin{split} C_0 = \overline{CX} \cdot \overline{CY} \cdot \overline{XY} = (\overline{C} \vee \overline{X})(\overline{C} \vee \overline{Y})(\overline{X} \vee \overline{Y}) = \overline{C} \vee \overline{X} \vee \overline{C} \vee \overline{Y} \vee \overline{X} \vee \overline{Y} = \overline{CX} \vee \overline{CY} \vee \overline{XY} = \\ = \overline{C} \vee \overline{X} \vee \overline{C} \vee \overline{Y} \vee \overline{X} \vee \overline{Y} = (C \vee X) \cdot (C \vee Y) \cdot (X \vee Y) = \overline{C} \overline{X} \cdot \overline{C} \overline{\overline{Y}} \cdot \overline{\overline{XY}}. \end{split}$$

It should be mentioned that four last forms are derived when 1-cubes are selected for the inversed terms, or for zeroed squares of the KM.

Consider the LE library that consists of only 2-input AND-NOT gates, or shortly, 2NAND gates. Then we select the AND-NOT/AND-NOT minimum normal form. We have to design the 3-input LN of the outer stage. Such a LN can

be implemented due to the formula:  $\overline{XYZ} = \overline{XYZ}$ . The resulting operator representation is  $C_0 = \overline{\overline{CX} \cdot \overline{CY}} \cdot \overline{\overline{XY}}$ , and it is implemented on 6 gates (Fig.1.7(c)). To minimize the LN some variables in the formula can be put out of brackets.

For example,  $CX \lor CY \lor XY = C(X \lor Y) \lor XY = C\overline{\overline{X} \cdot \overline{Y}} \lor XY = \overline{C\overline{\overline{X} \cdot \overline{Y}}} \cdot \overline{XY}$ . The resulting LN is shown in Fig.1.7 (d).

BF can be optimized by the method of decomposing by a variable. This method is based on the equation  $f(X_1, X_2, ..., X_n) = \overline{X_1} \cdot f(0, X_2, ..., X_n) \lor X_1 \cdot f(1, X_2, ..., X_n)$ . Here BFs with variable 0 and 1 are derived from respective halves of KM. In our example  $C_0 = \overline{C} \cdot C_0(0, X, Y) \lor C \cdot C_0(1, X, Y) = \overline{C}XY \lor C(X \lor Y) = XY \lor C(X \lor Y) = XY \lor C(\overline{X} \cdot \overline{Y} = \overline{\overline{XY}} \cdot \overline{C\overline{X} \cdot \overline{Y}}, \text{ i.e. we have$ derived the same LN as is shown in Fig.1.7 (d).

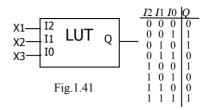

The optimization process is finished by the selection of better LN due to a set of criteria. As the simplest complexity criteron, the Quine complexity can be selected which is equal to the amount of all the gate inputs. This criterion was true for small scale ICs when their cost was proportional to their pin number. Now in the ASIC design each LE from the library has its area, which it occupies on the chip surface. Then the LN complexity is equal to the sum of all the LE areas. When LN is configured in FPGA then all LEs are mapped into 4-input lookup tables (LUTs) or logic cells (LCs). Then the LN complexity is equal to the number of used LUTs or LCs. In any case, there is the common practice to measure the complexity in the number of 2-input equivalent gates.

Comparing derived LNs in Fig.1.7 (c,d), we can see that their complexities are equal to 6 gates. But the complexity of the second LN is something less, because it contains more NOT gates. This LN can be used as the subnetwork of some complex LN, in which the variable sources and its invertors can be common for the whole LN. In this situation these NOT gates stay on the LN inputs. Therefore, they would not be considered.

The LN speed can be estimated as the number of gate stages in it, which is equal to the number of gates in the longest path from any input to any output of LN. Because the delay of CMOS circuits usually does not depend on the logic signal levels then we can not consider the input signal levels in the speed estimation. Comparing LNs in Fig.1.7 (c,d) shows that both of them have the delay of 4 gates. For real ICs the delay of a single gate is equal to 0,1 ns. Therefore, the delay of synthesized LNs is equal to 0,4 ns.

Due to the formula (1), the LN power consumption by clock frequency  $f_{\rm C}$ , and voltage *V* can be calculated on the base of gate fanouts and of average switching

activity  $E_s$ . When  $E_s$  is estimated to be 50%, then the power consumption is proportional to the sum of input numbers of all gates. For examples in Fig.1.7(c,d) these figures are equal to each other. More precisely the power consumption is calculated by simulation of the LN model with the real input data sets. Then the figure  $E_s$  is calculated precisely for each gate.

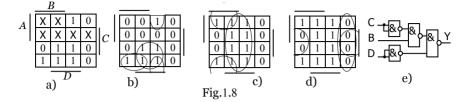

In many cases, BF is not defined on some subsets of input data. Such BF is called as **partially defined** BF. For example, in Fig.1.6, the trigger stimulating functions  $D_i$  would not be defined for the states which never occur in the network. They are called as prohibited states. Taking in consideration this situation, LN with minimized hardware can be derived. Consider the design of the LN for encoding of binary decimal code (BCD) to 7-segment LED display code. Such display has to view digits from 0 to 9, and another 6 possible combinations do not occur. The KM of BF for coding the third LED switching is shown in Fig.1.8 (a). Here unused subsets are marked by X sign and are "**don't care**" conditions.

The "don't care" conditions can be specified as either a 0 or a 1. Consider all of them are equal to a 0. Then we can select the proper cubes (Fig.1.8 (b)), and derive the following minimum normal form:  $Y = \overline{AD} \sqrt{ABC} \sqrt{BCD}$ . Note that KM is the unfolded 4-dimensional cube, and therefore, on KM the cut ellipses cover a single 1-cube. It can be proven that the distance between its terms is equal to 1. Here four squares, covered by the circle, form the 2-cube, which is reduced to  $\overline{AD}$ . We can assign the undefined states more speculative, to get the cubes of higher order (Fig.1.8(c)). The derived BF is  $Y=D \vee B\overline{C}$ , and is much simpler than the previous one. Its operator representation in the 2NAND operators is  $Y = \overline{\overline{D} \cdot \overline{BC}}$ . In such a manner, the inverse BF can be derived from the KM in Fig.1.8 (d):  $Y = \overline{\overline{B} \cdot \overline{D} \vee C \cdot \overline{D}} = \overline{\overline{D}(\overline{B} \vee C)} = \overline{\overline{D} \cdot \overline{BC}}$ , i.e. we get the same representation. The resulting LN is shown in Fig.1.8 (e).

In the CAD tools for the logic synthesis the BF optimization and its mapping into LN is made automatically without the designer interference. But many CAD tools can optimize complex BFs of more than 8-10 variables not optimally. It is explained by the fact that the logic optimization is the heavy combinatorial process, and for the affordable period of time the optimum solution could not be found. In this situation, the hand-made BF optimization may give better results. Besides, only selected CAD tools provide optimization of partially defined BFs (with "don't cares"). Therefore, the experienced designer must be able to optimize complex BFs by hand.

#### 1.4 Triggers

A **trigger** is a logic element that can hold one of *N* stable states. The most widely used trigger has N=2 states, and is named as binary trigger. The trigger is said to store the figure 0 (or 1) if it is in the state zero (one). The triggers are distinguished as latches and flip-flops. A **latch** is a trigger that can follow data variations and transfer them to an output line. It is characterized by two main properties: — it is transparent in that the output  $Q^t$  follows changes at the least part of the time t; — the storage is achieved using a bistable circuit, in which

| Table 1.5      |                |           |                      |  |  |  |

|----------------|----------------|-----------|----------------------|--|--|--|

| $\overline{R}$ | $\overline{S}$ | $Q^{t+1}$ | $\overline{Q}^{t+1}$ |  |  |  |

| 0              | 0              | ?         | ?                    |  |  |  |

| 0              | 1              | 0         | 1                    |  |  |  |

| 1              | 0              | 1         | 0                    |  |  |  |

| 1              | 1              | $O^t$     | $\overline{O}^t$     |  |  |  |

either Q=0 or Q=1 can be held.

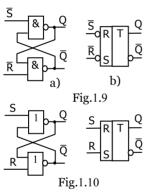

An **SR latch** has two inputs that are labeled *S* and *R*. This is associated with the quite general terminology "set" and "reset", that means that we force *Q* to a value 1 or 0. An SR latch can be built using two cross-coupled NAND gates, as shown in Fig.1.9 (a), and its symbol is shown in the Fig.1.9 (b). The algorithm of this latch is conveniently represented

by the Table 1.5, which is named as the function table. Here the symbol  $Q^{t+1}$  means the latch state at the moment of time t+1, i.e. after the switching process is finished, which is caused by the input signals, that were active at the moment t. From the latch equations  $Q = \overline{Q} \cdot \overline{S}$  and  $\overline{Q} = \overline{Q} \cdot \overline{R}$  (see the Table 1.5) the following equalities are derived:  $Q = \overline{\overline{Q} \cdot 1} = \overline{\overline{Q}}$  and  $\overline{\overline{Q}} = \overline{Q \cdot 1} = \overline{Q}$ , which are true for any Q. Therefore, when  $\overline{R} = \overline{S} = 1$  the state  $Q^{t+1}$  is fully derived from the previous state  $Q^t$ . The signal 0 at the output Q forces the signal 1 at the output  $\overline{Q}$ , which respectively keeps the signal Q=0 when it enters the input of NAND gate (see Fig.1.9). When

$\overline{R}=0$  and  $\overline{S}=1$  then the output signals are Q=0 and  $\overline{Q}=1$ , which stay stable after input signal exchange to  $\overline{R}=\overline{S}=1$ , because mentioned signals keep themselves. But when  $\overline{R}=\overline{S}=0$  the output signals are Q=1 and  $\overline{Q}=1$ , which after the event  $\overline{R}=\overline{S}=1$  are switched into one of possible states Q=0 and  $\overline{Q}=1$ , or Q=1 and  $\overline{Q}=0$ . The signals  $\overline{R}=\overline{S}=0$  cannot be simultaneously, because they force the indefinite latch operation.

The similar latch is built on the NOR gates, which is distinguished from the previous one by the direct inputs *R* and *S* (Fig.1.10).

In a complex digital system the designer must carefully control the flow of data to insure that the proper information is available to each block when it is needed. The common way to control the data movement within a network is to synchronize the system operation using a well-defined reference such as a clock signal. A **clock** is a control signal that periodically makes a transition from a 0 to a 1 and then back to a 0. The clock is usually denoted as *C* or *CLK*. Using a clock

signal to control the operation of a trigger provides us with the ability to dictate the times when data values can be stored in the device. This allows for the design of complex digital networks in which the data is moved in a synchronous manner.

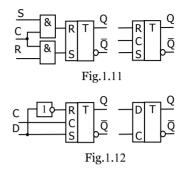

The network diagram of a clocked SR latch and its symbol are shown in Fig.1.11. Comparing this with Fig.1.9, we see that *C* is ANDed with both the *R* and *S* inputs. When C=1 the latch is operated as SR latch, accepting the information on the inputs *R* and *S*. When C=0 the

latch falls in the storing mode, in which the *R* and *S* inputs do not infer its state.

Two inputs *R* and *S* make the latch control complex, and afford two interconnection wires. This makes the disadvantage of the SR latch, which is absent in the D latch. A clocked **D latch** may be created in the same manner, as illustrated in Fig.1.12. As with the clocked SR latch above, the input is only active when C=1. The clocked D latch is often called a transparent latch due to its behavior during this time. Clocked latches are useful in synchronizing the data flow through a complex system. They also give more meaning to the name "latch" as they can be visualized as circuits that "latch on to" data when C=0.

The latches are never used as the triggers in the digital networks with the feedback like in Fig.1.6. For instance (see Fig.1.6), in some situation for the signal  $Z_1=0$ , LN generates the signal  $D_1=1$ , and for the signal  $Z_1=1$ , LN gives  $D_1=0$ . Then when latch *T*1 is opened by the clock, the high frequency oscillations occur due to the feedback chain, which traverses through the latch and LN.

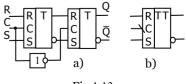

To prevent such a situation, the two staged triggers are used, named **flip-flops** (FFs). The simplest way to design the FF is cascading two clocked SR latches as it is shown in Fig.1.13 (a). The first latch is designated as the master circuit and is responsible for securing the input data *R* or S. The second latch acts as the slave. It is used to hold the value of the data that it receives from the master. The master and the slave circuits are controlled by opposite phases of the clock *C*. Since the master latch has *C* applied to it, it accepts inputs when *C*=1. The slave, on the other hand, uses  $\overline{C}$  for timing, so that it allows for changes in the inputs when *C*=0.

The value, that is transferred to the slave circuit (and hence to the output Q) is the value, that is in the master latch, when the clock makes a transition from C=1

to C=0. For this reason, this master-slave configuration is classified as being a falling edge-sensitive device. And such a trigger is the edge-triggered FF. In the FF symbol on the Fig.1.13 (b) such edge sensitive input is designated as '\'. The rising edge sensitive input is designated as '/'. Alternative designations for rising edge and falling edge

Fig.1.13

clock inputs are  $\triangleright$  and  $\triangleleft$ , respectively. Two letters T in the symbol associate with two latches in FF.

When the master latch is of D-type, then we derive the **D flip-flop**. The **JK flip-flop** is distinguished by the feedback in the master-slave circuit (see Fig.1.14). It behaves as the original SR flip-flop but when J=K=1 then FF exchanges its state to the opposite one, i.e.  $Q^{t+1} = \overline{Q^t}$ . JK-type FF used to be dominant in designs that were based on small scale one provide a state of the state of the state.

integration ICs, but can be useful now in some special networks.

The **toggle flip-flop** is a circuit that has a single input *T*. The operation of this FF is exactly as implied by its name: the output toggles whenever T changes from 0 to 1. When toggle FF has the edge sensitive clock input then its output toggles with each clock rising edge when T=1. Such FF is derived from JK-type FF when inputs J and K are coupled together. T flip-flop is a relatively special LE that does not have the versatility of FFs discussed above but may be useful, for example, in the counters.

FFs as well as latches are never designed as the networks of gates, because of unpredictable behavior of the derived circuits. This is explained by the fact that in modern circuits the delays in wires can supersede the gate delays. As a result, for example, the prohibited condition R=S=1 can occur in unexpected moments. Latches and FFs are usually designed as the transistor circuits when the proper technology gate library is formed. By this process, the complex problem of signal races both in gates and in wires between them is solved.

0

| Table 1.6 |   |   |       |                  |                  |  |  |

|-----------|---|---|-------|------------------|------------------|--|--|

| С         | J | K | $Q^t$ | D                | $Q^{t+l}$        |  |  |

| 0         | Х | Х | Х     | Х                | $Q^t$            |  |  |

| 1         | 0 | 0 | $Q^t$ | $Q^t$            | Qt               |  |  |

| 1         | 0 | 1 | Х     | 0                | 0                |  |  |

| ↑         | 1 | 0 | Х     | 1                | 1                |  |  |

| Î         | 1 | 1 | $Q^t$ | $\overline{Q}^t$ | $\overline{Q^t}$ |  |  |

K

j

c

&

&

DIT

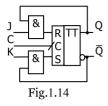

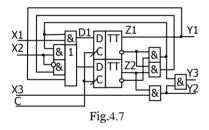

DFFs are most widely used. Additionally, they usually have *S* or *R* input, or both of them for asynchronous set or reset to the initial state. Very often DFFs have the enable input *CE*, which enables the FF clock sensitivity. Another FF types are designed on DFFs as on the component. Consider the design of JKFF. Its function table is the Table 1.6. Here the arrow means the clock rising edge, the letter X means the "don't care" state. The analysis of this table shows

that LN is needed which is attached to the input D of the FF. The respective KM is shown in Fig.1.15 (a), and the resulting FF network is illustrated by Fig.1.15 (b). Fig.1.16 illustrates the T-type FF based on D-trigger. In the following chapters

the main components of logic networks are described, which are based on logic gates and triggers.

16

#### 1.5 Decoders

The combinational network, which implements a set of BFs:

$$Q_{j} = A_{1}^{a^{1}} A_{2}^{a^{2}} \dots A_{n}^{a^{n}}, \qquad (6)$$

is named as **decoder** (DC), where  $j = 0,...,2^{n}-1$ ,  $A_i$  is the input variable, (i=1,...,n),  $a^i$  is the *i*-th digit of the binary representation of *j*.

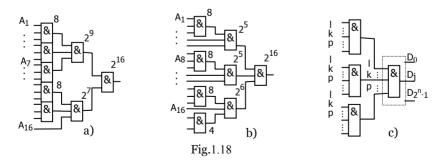

From (6) one can see that to develop the DC network the AND gates are needed. Consider the *p*-input AND gates, and the variables  $A_i$  and  $\overline{A_i}$  are generated out of DC. If  $p \ge n$  then the DC design is simple: this DC consists of  $2^n$  gates (see Fig.1.17), each of them implements one BF (6). If p < n then function  $Q_i$  has to be formed by dividing  $A_i$  to the sets of up to *p* variables. LN in which the

conjunctions are implemented in parallel has the highest speed. In Fig.1.18 (a) the DC network is drawn, which has the maximum speed, and which implements the 16-input AND function on the 3-input gates. Its delay is equal to 3*t*, where *t* is the gate delay. The number of gates is equal to 8. In general,

$$t(n,p) = [\log_{p} n]t, \ L(n,p) = [(n-1)/(p-1)], \tag{7}$$

where t(n,p) and L(n,p) are time delay and gate number of the LN, respectively, [x] means the nearest higher natural number of x. The whole DC network for 2<sup>n</sup> outputs contains 2<sup>n</sup>[(n - 1)/(p - 1)] of p-input gates. But such LN has large hardware volume. Firstly, it contains up to 2<sup>n</sup> conjunction gates, in this example, say  $A_1A_2A_3$ . Really, only eight such conjunctions are needed. Therefore, it would be better to take off the unnecessary gates. In Fig.1.18(a) the figures above the gate symbols show how many gates are really needed. Secondly, it can occur that some gate inputs in the last stages are not engaged (Fig.1.18 (a)). It would be better to divide the input variables into the sets to minimize the free gate inputs, as it is shown in Fig.1.18 (b).

The optimum solution of DC network (according to both speed and hardware volume) has the structure, represented in Fig.1.18(c). Its complexity is derived from the formula

$$C(n,p) = 2^{n} + \sum_{i=1}^{p} C(n_{i},p),$$

(8)

where  $n_i$  is the natural number, such that  $\sum_{i=1}^{p} n_i = n$ . The formula (8) achieves the minimum, when  $n_i$  has the value that is nearest to the value of n/p. Getting the optimum division of input digits to p groups, a set of decoders was designed. Their parameters are shown in the Table 1.6.

Table 1.6

| п              | 3 | 4     | 5     | 6     | 7     | 8     | 9     | 10         | 11                |

|----------------|---|-------|-------|-------|-------|-------|-------|------------|-------------------|

| ni             | 3 | 2,1,1 | 2,2,1 | 2,2,2 | 3,2,2 | 3,3,2 | 3,3,3 | 3,3(2,2,1) | 3,(2,1,1),(2,1,1) |

| <i>C</i> (n,3) | 8 | 20    | 40    | 76    | 144   | 276   | 536   | 1060       | 2096              |

Consider  $n_i \approx n/p$  then the equation (8) can be unfolded:

$$C(n,p) \approx 2^{n} + \sum_{i=1}^{p} C(n/p,p) = 2^{n} + pC(n/p,p) = 2^{n} + p2^{n/p} + p\sum_{i=1}^{p} C(n/p^{2},p) \dots$$

Then we derive the resulting equation:

$$C(n,p) \approx 2^{n} + p2^{n/p} + p^{2}2^{n/p^{2}} + p^{3}2^{n/p^{3}} + \dots$$

(9)

Consider n=11 and p=3, then due to three first items of the formula (9) C(11,3) = 2107, i.e. it gives rather good estimation, comparing to the Table 1.6. If the DC output number is represented as  $M=2^n$  then the equation (9) is represented in another form

$$C(n,p) \approx M + p \sqrt[p]{M} + p^{2} \sqrt[p^{2}]{M} + \dots$$

(10)

In many cases, it is useful to estimate the DC complexity as the sum of LE inputs. Such estimation is equal to the formula (10) multiplied by *p*:

$$C(n,p) \approx pM + p^2 \cdot \sqrt[p]{M} + \dots \quad (11)$$

The analysis of the formulas (7) and (11) shows that DC on 2-input LEs has the minimum hardware volume and maximum time delay, and DC on *n*-input LEs has the large hardware volume and the small time delay.

At present, small DCs with M<100 are implemented on PLA and CPLD. When designing ASIC, DC network is usually got from the library or it is generated by the special subprogram, or is synthesized from the behavioral description. The LEs of FPGA usually have the limited number of inputs (mostly 4). Therefore, to develop DCs in FPGA the designer must take into consideration the methods of DC network building.

#### 1.5 Multiplexers

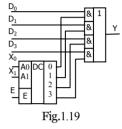

The combinational network which has up to  $2^n$  data inputs, one data output, and *n*-bit wide control input, which selects one of the data input, is usually named as an **multiplexor**. Consider the  $2^2 = 4$  – input multiplexor. Then its BF is

$$Y = E \cdot (D_0 \cdot \overline{X_1} \cdot \overline{X_0} \vee D_1 \cdot \overline{X_1} \cdot X_0 \vee D_2 \cdot X_1 \cdot \overline{X_0} \vee D_3 \cdot X_1 \cdot X_0), \quad (12)$$

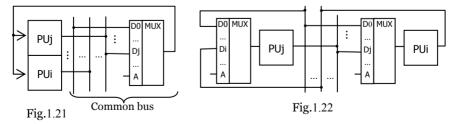

where *E* is the enable signal,  $D_i$  is the input data,  $X_1, X_0$  are digits of the selected data position. Comparing this equation and equation (6), one can find that multiplexor is the combination of DC, and AND/OR networks, which is illustrated by Fig.1.19.

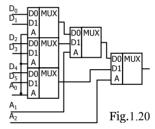

The standard 2- and 4- input multiplexers are usually in the project libraries. The large multiplexers are designed on the base of them as the multiplexor trees. The

example of the 6-input multiplexor, based on 2-input multiplexers, is shown in Fig.1.20.

In different projects the multiplexers are widely used to provide the sharing of the computational resources among different data sources. For example, they are inserted at the inputs of ALUs to put the input dates from different directions.

In ASICs the tri-state busses are implemented rarely because of their high cost and low reliability. Therefore, the common busses are made on the

multiplexor basis. In this situation the output of the *n*-input multiplexor is connected to all the bus destinations (for example, processor units – PUs). And the output of the *j*-th source is connected to the *j*-th input of the multiplexor, where  $j \le n$  (see Fig.1.21). The bus address to the multiplexor and the enable signals to destinations are formed by the arbiter network, which is not shown in Fig.1.21. As the simplest case of the common bus, consider the registered memory in which all the register outputs are connected together through the common multiplexor.

In more complex situations, any source can be connected to any destination. Then up to  $n \cdot n$  multiplexers are needed, as it is shown in Fig.1.22.

| Table 1.8           |       |       |       |       |   |

|---------------------|-------|-------|-------|-------|---|

| $D_9 - D_0$         | $A_3$ | $A_2$ | $A_1$ | $A_0$ | Р |

| 000000001           | 0     | 0     | 0     | 0     | 1 |

| 00000001 x          | 0     | 0     | 0     | 1     | 1 |

| 0000001xx           | 0     | 0     | 1     | 0     | 1 |

| 0000001xxx          | 0     | 0     | 1     | 1     | 1 |

| 000001xxxx          | 0     | 1     | 0     | 0     | 1 |

| 00001xxxxx          | 0     | 1     | 0     | 1     | 1 |

| 0001xxxxxx          | 0     | 1     | 1     | 0     | 1 |

| 001xxxxxx           | 0     | 1     | 1     | 1     | 1 |

| 01xxxxxxx           | 1     | 0     | 0     | 0     | 1 |

| 1 x x x x x x x x x | 1     | 0     | 0     | 1     | 1 |

| 0000000000          | х     | х     | х     | х     | 0 |

F1g.1.24

#### 1.6 Encoders

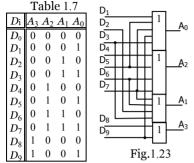

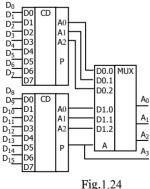

The **encoder** is a combinational network, which transforms the input data into the position of the most significant bit of this data. The example of the encoder is LN, which transforms the signals from the decimal button array to the **binary-decimal code** (BCD)  $A_3A_2A_1A_0$ , which represent the pushed button from 0 to 9 (see the Table 1.7). One of the possible LNs of such an encoder is shown in Fig.1.23. But when two buttons are pressed simultaneously then LN generates the incorrect code. For example, if  $D_5=D_6=1$  then  $A_3A_2A_1A_0=0111$ , that represents the signal  $D_7=1$ . Besides, it is impossible to recognize the pressed button, for example, the

button 0. To remove these disadvantages it is necessary to synthesize the **priority encoder**. Such encoder always forms the code of a single pressed button, for instance, more significant one. The

button, for instance, more significant one. The Table 1.8 is the truth table of such an encoder. When any button is pressed then the output bit P=1. The proper Boolean equations are

$$A_3 = D_9 \lor D_8, A_2 = (D_9 \lor D_8)(D_7 \lor D_6 \lor D_5 \lor D_4)$$

$$A_1 = (\overline{D_9 \lor D_8})((D_7 \lor D_6) \lor (\overline{D_5 \lor D_4})(D_3 \lor D_2),$$

$$A_0 = D_9 \lor \overline{D_8}(D_7 \lor \overline{D_6}(D_5 \lor \overline{D_4}(D_3 \lor D_2D_1))),$$

$P=D_0 \lor D_1 \lor A_3 \lor A_2 \lor A_1.$

To build many input priority encoders the hierarchical LN is used, which consists of small encoders. Consider we have the encoder unit, which is built due the previous equations, but the inputs  $D_8$ ,  $D_9$  are not used (zeroed). Then one of possible 16-input encoders is shown in Fig.1.24.

Here the multiplexor selects the group of bits, which is generated by the activated coder, which has the higher priority. Due to these principles, the priority encoders are built, which are used, for example, as interrupt encoders. Another example is LN which finds the number of zero bits before the

most significant bit in the mantissa during its normalization.

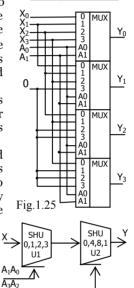

#### 1.7 Shifters

The **shifter** is a combinational network, which transfers the input word to the output with the shift of its bits. The Table 1.9 shows how the logic right shift of the 4-bit word X is implemented in the shifter, giving the output word Y.

The shift bit number is given by the word  $A_1A_0$ . Due to the logic shift, the bit, which is shifted in, is zero. In the case of the arithmetic shift, the left shifted bit would be the sign bit, here  $X_3$ . It is useful to build the shifters on the base of the multiplexor. Such shifter, which implements this algorithm, represented by the Table 1.9, is illustrated by Fig.1.25.

According to this principle, the shifter up to n-1 digits is based on the *n*-input multiplexers. But when *n* is larger than 6–8 then the hardware volume is too high. In this situation the multistage shifters are formed.

One can design the shifter to 0, 4, 8, and 12 bits based on 4-input multiplexers. Then the complex shifter consists of such shifter, named as U1, and the usual shifter to 0,1,2,3 bits, named as U2. Such a shifter is illustrated by Fig.1.26. Here the bit shift number is given by the code  $A_3A_2A_1A_0$ . The most significant bits  $A_3A_2$  control the shifter U2 and disits  $A_3A_2$  control the

shifter U2, and digits  $A_1A_0$  control the shifter U1. Consider we have to shift the code *X* to 13=1101 bits. Then the shifter U1 shifts it to 1 bit, and the shifter U2 shifts it to 12 bits.

#### 1.8 Binary adders

Binary **adders** or **summators** (shortly SM) are used for addition of binary integer numbers

$$Q = B + D$$

, where  $B = B_{n-1}2^{n-1} + ... + B_12 + B_0$ ,  $D = D_{n-1}2^{n-1} + ... + D_12 + D_0$ .

The combinational binary adders, which consist of one bit adders (**full adders**), are mostly used. The Table 1.10 is the truth table of such full adder. Here  $Q_i$  is the sum of *i*-th bits  $B_i$  and  $D_i$ ,  $C_i$  is the **carry** bit to the *i*-th bit. KM for the output  $C_{i+1}$  is illustrated by the Fig.1.7(b) for  $X = B_i$ ,  $Y = D_i$ . And the proper Boolean equation is  $C_{i+1} = B_i D_i \lor B_i C_i \lor D_i C_i$ . KM for the output  $Q_i$  is illustrated by the Fig.1.5(b) for  $X_1 = B_i$ ,  $X_2 = D_i$ ,  $X_3 = C_i$ . Therefore, this BF could not be simplified, and is equal to  $Q_i = B_i D_i C_i \lor B_i \overline{D_i} \overline{C_i} \lor \overline{B_i} \overline{D_i} \overline{C_i}$ . Additionally, BF  $\overline{C_{i+1}}$  is needed to simplify the circuit of the (*i*+1)-th stage of the adder. The respective network occupies 10 gates.

| Table 1.9 |       |       |            |       |       |       |

|-----------|-------|-------|------------|-------|-------|-------|

|           | $A_1$ | $A_0$ | $Y_3$      | $Y_2$ | $Y_1$ | $Y_0$ |

|           | 0     | 0     | <i>X</i> 3 | $X_2$ | $X_1$ | $X_0$ |

|           | 0     | 1     | 0          | $X_3$ | $X_2$ | $X_1$ |

|           | 1     | 0     | 0          | 0     | $X_3$ | $X_2$ |

|           | 1     | 1     | 0          | 0     | 0     | $X_3$ |

| Table 1.10 |         |         |           |             |

|------------|---------|---------|-----------|-------------|

| $B_{i}$    | $D_{i}$ | $C_{i}$ | $C_{i+1}$ | $Q_{\rm i}$ |

| 0          | 0       | 0       | 0         | 0           |

| 0          | 0       | 1       | 0         | 1           |

| 0          | 1       | 0       | 0         | 1           |

| 0          | 1       | 1       | 1         | 0           |

| 1          | 0       | 0       | 0         | 1           |

| 1          | 0       | 1       | 1         | 0           |

| 1          | 1       | 0       | 1         | 0           |

| 1          | 1       | 1       | 1         | 1           |

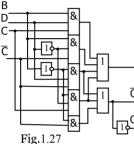

But BFs can use common terms, as in the following equations

$$Q_{i} = B_{i}D_{i}C_{i} \lor B_{i}\overline{D}_{i}\overline{C}_{i} \lor \overline{B}_{i}D_{i}\overline{C}_{i} \lor \overline{B}_{i}\overline{D}_{i}C_{i},$$

$$\overline{C}_{i+1} = \overline{D}_{i}\overline{C}_{i} \lor \overline{B}_{i}D_{i}\overline{C}_{i} \lor \overline{B}_{i}\overline{D}_{i}C_{i}, \quad C_{i+1} = \overline{\overline{C}}_{i+1}.$$

The resulting network is drawn on the Fig.1.27, and it occupies only 8 gates, to say nothing about input invertors. The carry signal propagates through 3 gates. The *n*-bit adder is shown on the Fig.1.28. It is named as **ripple-carry** adder

because of the ripple-carry scheme to transfer the carry bits. To perform the addition the input carry bit is  $C_0 = 0$ . Such an adder consists of *n* full adder stages and has the delay 3nt, where *t* is the gate delay.

Qi Table 1.11  $B_0 D_0 C_0$  $B_1 D_1$ B<sub>n-1</sub> D<sub>n-1</sub> D  $C'_{i+}$ Q FA FA 0 0 0 0 n-1 1 0 1 0 1 1 0 0 1 Qn-1  $Q_1$  $Q_0$ 1 1 1 0 Fig.1.28

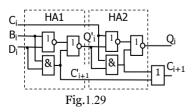

This delay can be decreased, and the hardware volume of the full adder can be minimized when it is implemented on two **half adders** (HAs). The HA adds two bits due to the truth Table 1.11. The following BFs describe it.

$$Q'_i = B_i D_i \vee \overline{B_i \vee D_i}, \quad C'_{i+1} = B_i D_i.$$

Then the carry bit to the (*i*+1)-th digit can be formed due to the BF:  $C_{i+1} = C'_{i+1} \vee C''_{i+1}$ , where  $C'_{i+1}$  and  $C''_{i+1}$  are the carry bits caused by the addition of couples of digits  $B_i$ ,  $D_i$ , and  $Q'_i$ ,  $C_i$ . The Fig 1.29 illustrates the resulting network.

To increase the adder speed the parallel carry networks are designed. Such a network calculates the carry bit for the group of *m* digits using the two staged logic circuits. The adder is divided to k=[n/m] groups of parallel adders, each of them has its own parallel carry network. The resulting adder delay is estimated as *kt*, where *t* is the delay of the parallel carry network. The development of parallel

carry networks by the designer is a bad praxis. Such a network has a lot of lines, which correct routing is very hard, because the line propagation delays can be much higher than gate delays. The common praxis is to use the fast speed adders as ready-to-use library components. The subtraction function is usually performed using the 2-s complement approach. **2-s complement** of *n* bit binary number  $D \neq 0$  is defined as

$${D}_2 = 2^n - D = (2^n - 1 - D) + 1 = (1...11 - D) + 1.$$

The number in brackets is **1-s complement** of *D*, which is formed by inversion of all the bits of the number *D*. The subtraction is calculated as  $B-D=B+{D}_2$ . Therefore, to implement the subtraction, the second number has to be inverted, and a 1 is added to the sum.

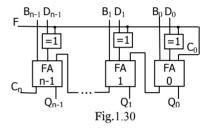

In applications both addition and subtraction are required. A single adder/ subtractor unit can be built using the ripple-carry adder discussed above. This unit is shown in Fig.1.30. Inspecting the logic diagram shows that 2 basic modifications have been made to the original adder in Fig.1.28. First, each *D*<sub>i</sub> input line

has an XOR gate in its path. Second, a new control bit F has been added to the circuit, which is connected to each XOR and also to the carry-in bit of the adder. The circuit acts as an adder when F=0, and as subtractor when F=1. In the second situation XOR gates work as invertors and carry-in bit is a 1, which is added to the sum.

#### 1.9 Registers

**Register** (RG) is a set of triggers, which have a common control network. A single trigger can be considered as the one bit wide register. Therefore, triggers often are named as registers as well. RG is used for data storing and implementation of some operations with them. The bit wise logic operation with the word Q in RG and the word D at its inputs is such operation. Another operations are different shift operations and data output.

RG is considered to be a logic network, which consists of a trigger set (plain register) and logic network (LN) which implements the output functions and functions of trigger stimulating (see Fig.1.6). The RG design consists in selection of the trigger type and in LN synthesis.

When the computing system with RGs is designed, one has to take in considerations the properties of the clock propagation system. Each modern LSI circuit has one or small number of clock propagation trees. Such a tree provides the stable clock signal to each trigger with the minimum clock skew. The **clock skew** is the delay between the edge of the clock signal, which enters the trigger, and the base moment of time. Only when the clock skew is zero, the minimum clock period is estimated as the maximum delay from output of one trigger to the input of another one plus the trigger delay. Thank to this feature, the proving of the design correctness is assured for the circuit with thousands or millions of triggers. Considering this feature of the clock propagation system, in most of cases RGs are implemented on flip-flops.

| Table 1.12                                                                  |   |   |   |       |                 |

|-----------------------------------------------------------------------------|---|---|---|-------|-----------------|

| C                                                                           | R | S | W | D     | $Q^{t+l}$       |

| 0                                                                           | Х | Х | Х | Х     | $Q^t$           |

| 1                                                                           | 0 | 0 | 0 | $Q^t$ | $\frac{Q^t}{0}$ |

| $\uparrow$                                                                  | 1 | 0 | Х | 0     | 0               |

| $\uparrow$                                                                  | 0 | 1 | Х | 1     | 1               |

| 1                                                                           | 0 | 0 | 1 | DI    | DI              |

| <b>↑</b>                                                                    | 1 | 1 | Х | Х     | Х               |

| $ \uparrow        X X X X$ $R  \frac{S}{X X 0 0}$ $a) W$ $S$ $C$ $Fig.1.31$ |   |   |   |       |                 |

To provide the minimum clock skew it is not recommended to attach any logic circuit to the clock input of the trigger. Besides, when the races of the control signals occur, such circuit can generate glitches. The glitch is a short, needle formed impulse, which forces the incorrect trigger switching. Instead of controlling the clock signal, the enable input of the trigger is usually used.

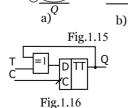

Consider the design of RG with the functions of set, reset, and write (control signals S, R, W, respectively) based on the D-triggers. The table 1.12 is its truth table, and respective WD is shown in Fig.1.31(a). Here the signals S, R have higher priority. The resulting stimulating function for the *i*-th digit of RG is the following:

$$D = S \vee \overline{R} \cdot W \cdot D_{\mathrm{I}} \vee \overline{R} \cdot \overline{W} \cdot Q.$$

Fig.1.31 (b) illustrates the *i*-th bit of the register.

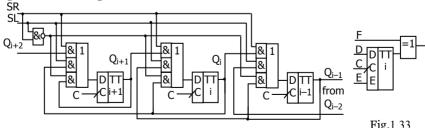

The shift operations in RG can be implemented as left and right shifts to 1, 2,... bits. Fig.1.32. represents a part of the **shift** RG with operations of left shift (SL),

and right shift (SR) to a single bit. When the left shift operation, the *i*-th output is connected to the (i+1)-th input of RG. The input data *DL* is shifted in the first bit. When the right shift, the input data *DR* is loaded into the (*n*-1)-th bit, *i*-th output is connected to the (*i*-1)-th input of RG. Note, that  $DL=Q_{i-2}$ ,  $DR=Q_{i+2}$  when n=3(see Fig.1.32). When shifts are not done, i.e. when  $\overline{SR \vee SL} = 1$ , then the *i*-th input and output of RG is connected together to provide the information storing.

As was shown in the previous chapter, the subtraction is calculated through the 2-s complement of the data. For this purpose, in some operational units the data registers are used which outputs the direct or inverse code depending on the addition or subtraction operation. A single bit of such RG is shown in Fig.1.33. This is an example of RG with data output operation. The input E enables the register data storing.

Fig.1.32

Fig.1.33

#### 1.10 Counters

**Counter** (CTR) is a logic unit which implements the increment or decrement operation to 1, 2, etc., and data storing. As any logic circuit, it can be designed as a finite state machine (FSM). But there are some methods of the CTR synthesis, which use its operation specific.

The CTR is a network with FFs. Therefore, the CTR synthesis must obey the rules of the FF synchronization, which were mentioned in the previous section. For example, two decades ago the method of sequential counters was widely used. Such counters are based on asynchronous T-triggers, which are connected sequentially in a chain. In this situation, each trigger is considered to have its own clock signal, which feeds its T-input. When such a CTR is implemented in the LSI circuit, then its design is complicated, and its operation can be unstable.

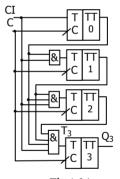

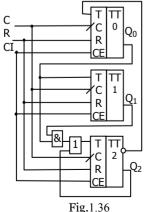

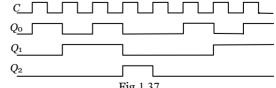

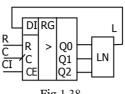

To prevent this situation, the synchronous T-type FFs are used. A set of such FFs form the specific RG, which bits can be negated synchronously by the clock edge. Consider the count impulse  $C_{\rm I}$  comes to the T input of the first FF, and its stimulating signal is  $T_0 = C_{\rm I}$ . Then its output  $Q_0$  exchanges its state every impulse  $C_{\rm I}$ , i.e. every second impulse  $Q_0 = 1$ . The output of the second FF has to be exchanged every second impulse  $C_{\rm I}$ , i.e. its stimulating signal has to be  $T_1 = Q_0C_{\rm I}$ . The resulting signal functions of CTR triggers are the following:

$$T_0 = C_{\rm I}, T_1 = Q_0 C_{\rm I}, T_2 = Q_1 Q_0 C_{\rm I}, ..., T_i = Q_{i-1} Q_{i-2} \dots Q_0 C_{\rm I}.$$

The respective 4-bit CTR network is shown in Fig.1.34. Here the signal on the FF input T enables the operation +1 modulo 2. Such CT has the name of parallel carry CTR because the carry signal (here  $T_i$ ) to the *i*-th bit is formed in parallel by the AND gate.

The usual *n*-bit wide counter repeats its states after  $2^n$  input impulses. Such CTR is said to have the period (modulo) equal to  $2^n$ . Often the CTR counting period has to be not equal to  $2^n$ . Such CTRs are designed by excluding the spare states. This is usually achieved by jumping round such states.

Consider the CTR with a period of k=5 cycles. To design such a CTR  $n=[\log_2 k] = 3$  FFs are needed. The states of the CTR with the period of 8 cycles are represented by the table 1.13. Let three last states are to be excluded. Then to go round these states the following states are selected: the state before the first excluded state  $A=(a_2,a_1,a_0) = (1,0,0)$ , the first excluded state  $B=(b_2,b_1,b_0) = (1,0,1)$ , the last excluded state but the next one  $C=(c_2,c_1,c_0) = (0,0,0)$ .

In the usual counter after the state *A* goes the state *B*, but in this CTR the jump from *A* to *C* has to be done. Then by the analysis of bits  $a_i$ ,  $b_i$ ,  $c_i$  in the *i*-th digit the correction of the

Fig.1.34

| Table 1.13 |       |       |       |  |

|------------|-------|-------|-------|--|

| $Q_2$      | $Q_1$ | $Q_0$ | State |  |

| 0          | 0     | 0     | С     |  |

| 0          | 0     | 1     |       |  |

| 0          | 1     | 0     |       |  |

| 0          | 1     | 1     |       |  |

| 1          | 0     | 0     | Α     |  |

| 1          | 0     | 1     | В     |  |

| 1          | 1     | 0     |       |  |

| 1          | 1     | 1     |       |  |

stimulating function of the *i*-th FF is found. The three situations are distinguished, when  $b_i = c_i$ ;  $b_i \neq c_i = a_i$ ; and  $b_i \neq c_i \neq a_i$ .

In the first situation the correction of the stimulating function is not needed, because jumps  $a_i \rightarrow b_i$  and  $b_i \rightarrow c_i$  are equal to each other because of  $c_i = b_i$ . In the second one the stimulating function provides the storing mode, due to  $c_i = a_i$ . And in the third one it implements the inversion, because of  $c_i \neq a_i$ , i.e.  $c_i = \overline{a_i}$ .

When C is all zero state, then such correction is implemented by forming the function  $F = Q_{n-1}^{a_{n-1}} \cdots Q_{n-1}^{a_1} Q_0^{a_0}$ , which is equal to a 1 only for the set  $(a_2, a_1, a_0)$ . Consider we have the T-type FFs. Then the stimulating functions are corrected

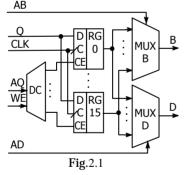

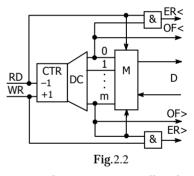

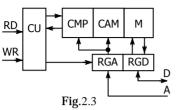

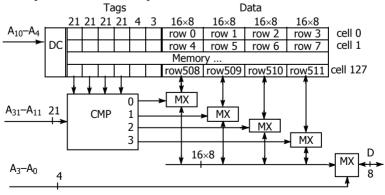

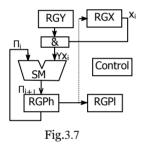

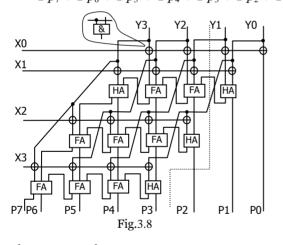

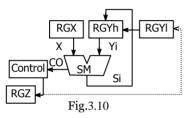

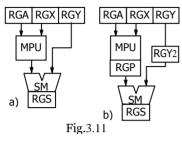

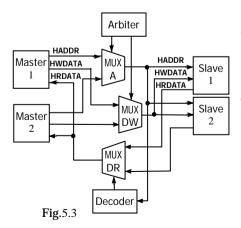

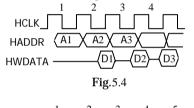

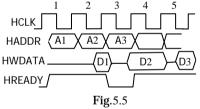

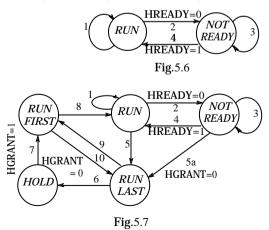

due to the rule: