VHDL лаборатория. Программирование ПЛИС . Программирование на VHDL.

|

|

| |

| Помощь |

Модуль SQRT выполняет модифицированный алгоритм на основе сдвига и вычитания с восстановлением остатка.

Целью алгоритма является получение приближения двоичного числаBi = 0,b1b2…bi0…0 к значению √x .

Он основан на проверке знака остатка Ri = x - Bi2, в результате чего выбирается очередная цифра bi.

В модифицированном алгоритме первые k итераций не выполняются, а результаты k - той итерации находятся при помощи табличных функций.

Такими табличными функциями являются:

Bk = fB(xk) ≈ √xk ; Rk' = fR(xk) ,

где xk - 2k старших розряда входного данного x, причем

Rk = Rk' + x - xk

Например, на рис.1 показана функциональная схема, которая выполняет модифицированный алгоритм для 12-разрядных входных данных, n = 6 - разрядного результата и k = 3. При этом табличные функции fB и fR реализованы в блоках постоянной памяти ROMB и ROMR, соответственно.

Рис.1 Схема блока извлечения квадратного корня

Благодаря применению блоков постоянной памяти, в данном случае удалось уменьшить количество итераций с шести до четырех, первая из которых – это обращение к этим блокам. Соответственно, схема извлечения корня стала меньшей на три сумматора и три мультиплексора.

Недостаток модифицированного алгоритма состоит в том, что блоки постоянной памяти должны иметь 2k-разрядные адресные входы. Поэтому они имеют значительный объем при большом k.

Впрочем, этот алгоритм целесообразно использовать в современных ПЛИС при k ≤ 6. Так, при k= 3 для n = 24-разрядных данных параметри блока квадратного корня приведены в табл.5.1., то есть с применением этого алгоритма параметры блока квадратного корня улучшаются.

В генераторе виртуальных модулей квадратного корня организован ввод таких параметров, как разрядность входных и выходных n данных, разрядность 2k адресов блоков постоянной памяти, наличие входного и выходного регистров, построение полностью конвейеризованой и частично конвейеризованой схемы, то есть с n - k или с ](n - k)/2[ ступенями конвейера. При этом пользователю даются оценки аппаратных затрат модуля и максимальной тактовой частоты.

Сгенерированный модуль SQRT предназначен для рассчитывания квадратного корня для целого аргумента. То есть, при входной разрядности 2n старшие n розрядов результата представляют целую часть числа, а остальные разряды – дробную часть.

Разрядностью входных ('Разрядность входа') и выходных ('Разрядность выхода') данных могут быть любые целые числа больше четырех

Если не выбрано кнопку 'Вход синхросигнала', то модуль SQRT генерируется как комбинационная схема без регистров. Когда она выбрана, то в схему блока вставляется набор регистров.

При выборе переключателя 'Регистры на входе и выходе', два регистра будут установлены на входе и выходе модуля. При выборе переключателя 'Каждые 2 ступени с регистром' дополнительные конвейерные регистры устанавливаются между каждыми двумя степенями структуры модуля. При выборе кнопки 'Каждая ступень с регистром' максимальное число конвейерных регистров устанавливается в модуле. Очевидно, что конвейерные регистры обеспечивают увеличение максимальной тактовой частоты модуля за счет увеличения латентной задержки.

Выбрав кнопку 'Разрешение синхросигнала' можно добавить в схему модуля вход CE, который контролирует тактовый сигнал. Этот вход используют для замедления работы модуля.

Структура модуля SQRT отличается тем, что от одной до пяти первых итераций алгоритма вычисления корня реализованы с использованием логических таблиц LUT. Разрядность адреса ЛТ выбирается в окне 'Разрядность адреса LUT'. Максимальная разрядность адреса равна десяти. Следует отметить, что современные ПЛИС фирм Xilinx, и Altera построены на 6-разрядных ЛТ.

При выборе кнопки 'Показать характеристики' выводятся приближенные характеристики модуля SQRT для избранных входных параметров. Это объем аппаратных затрат, латентная задержка в тактах и максимальная тактовая частота для ПЛИС типа Xilinx Spartan-6. Эти характеристики приведены только для справки. Более точные характеристики могут быть получены только после конфигурирования этого модуля в конкретной ПЛИС.

Следует отметить, что если выбраны 10-разрядные ЛТ, а синтез схемы направлен на использование блоков памяти BlockRAM то реальные аппаратные затраты намного меньше, чем приведенные для оценки.

При выборе кнопки 'Модуль вывести на экран' на экран выводится VHDL-код сгенерированного модуля. Текст этого кода может быть перемещен в среду пользователя с помощью экранных функций Select, Copy и Paste.

Сгенерированные виртуальные модели могут быть сконфигурированы в ПЛИС всех компаний-производителей и большинства типов. В таблице 1 приведены средние параметры модуля SQRT, которые сконфигурированы для некоторое ПЛИС фирмы Xilinx. Приведенные параметры полученные для 16-разрядных входных и выходных данных без особых настроек файла ограничений для синтеза, размещения и трассировки.

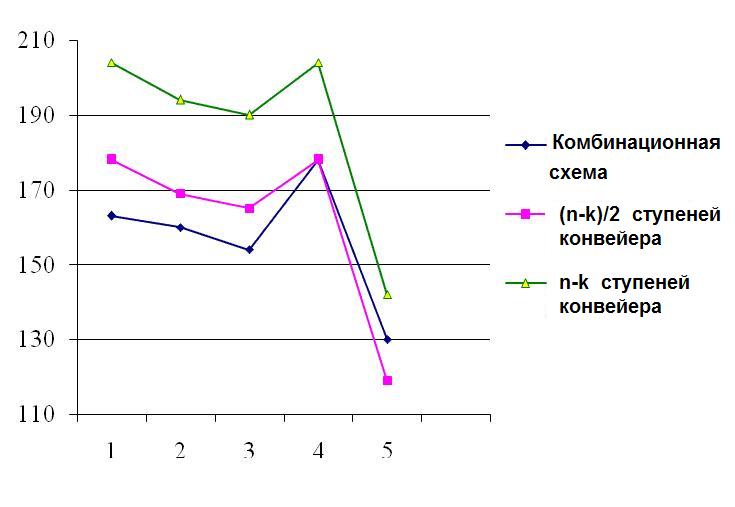

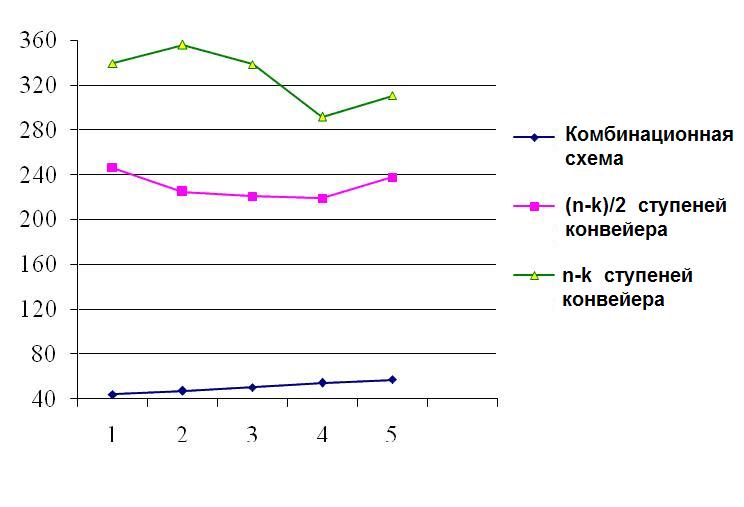

После синтеза и размещения модулей блока квадратного корня в ПЛИС Xilinx Spartan-6 было получено ряд характеристик аппаратных затрат (рис.2) в количестве ЛТ и максимальной тактовой частоты, МГц (рис.3) для различных значений k при входной разрядности 24 и разрядности результата n = 12 Рассматривались модули в виде комбинационной схемы, полностью конвейеризованные и частично конвейеризованные модули.

Таблиця 1. Параметри модуля SQRT

| Параметр | Конвейеризация | Virtex-4 | Spartan-6 | Virtex-7 |

| Аппаратные затраты, ЛТ | Без конвейеризации | 281 | 277 | 309 |

| Аппаратные затраты, ЛТ | Половинная конвейеризация | 269 | 214 | 238 |

| Аппаратные затраты, ЛТ | Полная конвейеризация | 292 | 275 | 302 |

| Тактовая частота, МГц | Без конвейеризации | 35 | 32 | 62 |

| Тактовая частота, МГц | Половинная конвейеризация | 196 | 174 | 333 |

| Тактовая частота, МГц | Полная конвейеризация | 298 | 271 | 552 |

Рис.2. Аппаратные затраты блока √x x в зависимости от k

Рис.3 Максимальная тактовая частота блока √x в зависимости от k