Что такое VHDL ?

| Назад | Cодержание | Следующая |

Изучение VHDLЧто такое VHDL ?Кратко о VHDL. Традиционно одним из этапов пректирования средств вычислительной техники является разработка электрических схем. Эта ответственная работа связана с большими трудозатратами, контролем правильности и соответствия задуманному проекту, необходимостью четкого и емкого описания созданных схем, трудностями с их сопровождением и модернизацией. САПР вычислительной техники, как правило, имеют средства ввода и редактирования схем. Однако два десятилетия назад при разработке СБИС отказались от схемного проектирования. Язык Very high speed integrated circuits Hardware Description Language (VHDL) был разработан в 1983 г. по заказу Министерства обороны США с целью формального описания логических схем для всех этапов разработки электронных систем, начиная модулями микросхем и кончая крупными вычислительными системами. Он является стандартным языком с 1987 г. Стандартом 1993 г. закреплены многие его усовершенствования [1]. Наряду с языком Verilog он является базовым языком при разработке аппаратуры современных вычислительных систем. В чем преимущества VHDL над схемным проектированием?Проектирование больших вычислительных устройств (ВУ) — С помощью VHDL проще и быстрее ввести и проверить большой проект. Десятью строками VHDL можно описать как 1, так и 100000 триггеров. Микросхему с интеграцией более 10000 вентилей разработать только с помощью электрических схем очень трудно по причине громоздскости схем. Проект на VHDL -объединение структуры ВУ и алгоритма его функционирования. Для ВУ, описанного на VHDL, необязательно выполнять проверку правильности его функционирования, например, путем его макетирования. Чтобы определить, правильно ли ВУ выполняет заданный алгоритм, достаточно его VHDL -программу запустить на исполнение в симуляторе VHDL. Соответствующие САПР преобразуют VHDL-описание в комплект документации для изготовления работоспособного устройства. Проект на VHDL — самодокументированный, т.е. он не требует дополнительного технического описания или в виде схем. Нечеткость и небрежность описания исключаются, так как проект на VHDL несложно проверить. Высокая надежность проекта. Синтаксический анализ, моделирование и компиляция в логическую схему быстро выявляют ошибки проекта. Проект на VHDL — универсальный проект. Разработанный однажды вычислительный блок может быть использован во многих других проектах. При этом многие сруктурные и функциональные параметры блока могут быть настраиваемыми (параметры разрядности, объема памяти, элементная база, состав блока и структура межсоединений). Проект на VHDL — портативный проект. Разработанный для одной элементной базы, проект ВУ без труда переносится на другую элементную базу, напр. СБИС с различной технологией. Проект на VHDL — долгоживущий проект. Электрическая схема всегда разрабатывается под конкретные элементную базу и интерфейс. Так как элементная база сменяется за период 2-5 лет, за этот же период устаревают и электрические схемы, ее использующие. Проект ВУ на VHDL может быть повторно использован через несколько лет. Хорошее техническое решение (напр., изобретение), описанное на VHDL, может быть востребованным в течение десятилетий. VHDL — универсальное средство описания ВУ на уровнях:

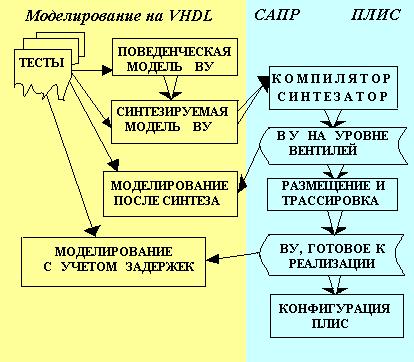

Ход проектирования с использованием VHDL.На рисунке показана схема разработки проекта ВУ, предназначенного для исполнения в программируемой логической интегральной схеме (ПЛИС).

Вначале ВУ описывается в виде своей поведенческой модели, на которой отрабатывается задуманный алгоритм функционирования ВУ. Затем эта модель вручную перерабатывается в синтезируемую модель ВУ, описанную на уровне регистровых передач. Такая модель, будучи странслированной компилятором-синтезатором, дает проектную документацию в виде файла описания схемы ВУ на уровне вентилей (EDIF — файл). При этом автоматически выполняется логическая оптимизация ВУ. Одновременно этот файл автоматически преобразуется в VHDL- модель ВУ на уровне вентилей. Проект ВУ в виде Electronic Distribution International Format (EDIF) — файла принимается как исходный всеми САПР изготовления ПЛИС и СБИС. Эти САПР выполняют замену вентилей на библиотечные компоненты, их размещение на площади кристалла, трассировку межсоединений, проектирование масок, проверку соответствия проектным нормам и т.п. В результате записываются файлы проектной документации изготовления кристалла и его логической модели, учитывающей задержки как в вентилях, так и в межсоединениях. Эта модель также представляется на VHDL. Стоимость ошибок при проектировании СБИС очень высока, особенно на ранних этапах. Поэтому все этапы проектирования — алгоритмический, структурный, логический, технологический — сопровождаются моделированием ВУ с помощью, так называемого испытательного стенда (testbench). Этот стенд представляет собой VHDL-модель, составными частями которой являются модель тестируемого ВУ и модели генератора тестовых сигналов и логического анализатора, проверяющих правильность функционирования ВУ. Причем на всех этапах может использоваться один и тот же испытательный стенд и те же тестовые файлы. По каким причинам VHDL используется в современных САПР микроэлектроники?Исторически сложилось, что в микроэлектронной индустрии наибольшее распространение получил язык Verilog. Полтора десятилетия назад этот язык выиграл конкурентную борьбу с другими языками задания ВУ, благодаря небольшим требуемым вычислительным ресурсам прежних рабочих станций и достаточно точным результатам моделирования СБИС. VHDL — более универсальный и гибкий язык, но он проигрывал в быстродействии языку Verilog, особенно при моделировании на уровне вентилей и транзисторов. VHDL получил широкое распространение в университетах и исследовательских учреждениях, так как это строгий, стройный, универсальный и расширяемый язык. Так, например, появились пакеты VHDL для аналогового моделирования, моделирования многозначной логики. Кроме того, симуляторы VHDL были гораздо дешевле симуляторов Verilog. Все современные САПР микроэлектроники имеют компиляторы как с Verilog, так и с VHDL. Программист, освоивший VHDL, без особого труда может перейти к программированию на языке Verilog. В отличие от обратного. Важнейшими качествами VHDL в САПР выступают следующие:Гибкость. Проект, описанный на VHDL, может быть легко настроен под конкретные задачи потребителя. Универсальный язык. VHDL — общепринятый язык для всех основных фирм — изготовителей микросхем ПЛИС, ПЛМ, заказных СБИС как стандартный язык для задания сложных проектов. Проектирование с VHDL — устойчивая тенденция в инженерной технологии. Существуют компиляторы, транслирующие VHDL- программы в эквивалентные им Verilog — программы. Моделирование с учетом задержек. Фирмы — изготовители микросхем в своих САПР обеспечивают генерацию моделей результатов размещения и трассировки, описанных на VHDL. Стандартное подключение блоков. Конструкции языка, такие как entity, port map, configuration, обеспечивают надежную и быструю стыковку блоков, разработанных разными фирмами и разработчиками, в различном сочетании. Стандартное тестирование. На всех этапах разработки выполняется тестирование по одной методике одними и теми же тестами. VHDL — стандарт будущего. Все новые САПР основаны на технологии трансляции описания ВУ на языке описания аппаратуры. Использование VHDL — гарантия того, что через 5 и 10 лет найдется САПР, поддерживающая старые разработки.

Анатолий Сергиенко |

| Назад | Cодержание | Следующая |