VHDL лабораторія. Програмування ПЛІС . Програмування на VHDL.

|

|

| |

| Допомога |

Модуль SQRT виконує модифікований алгоритм на основі зсуву та віднімання з відновленням остачі.

Метою алгоритму є одержання наближення двійкового числаBi = 0,b1b2…bi0…0 до значення √x .

Він оснований на перевірці знаку остачі Ri = x - Bi2, у результаті чого вибирається чергова цифра bi.

У модифікованому алгоритмі перші k ітерацій не виконуються, а результати k - тої ітерації знаходяться за допомогою табличних функцій.

Такими табличними функціями є:

Bk = fB(xk) ≈ √xk ; Rk' = fR(xk) ,

де xk - 2k старших розряди вхідного данного x, причому

Rk = Rk' + x - xk

Наприклад, на рис.1 показана функціональна схема, яка виконує модифікований алгоритм для 12-розрядних вхідних даних, n = 6 - розрядного результату та k = 3. При цьому табличні функції fB та fR реалізовані у блоках постійної пам’яті ROMB та ROMR, відповідно.

Рис.1 Схема блоку добування квадратного кореня

Завдяки застосуванню блоків постійної пам’яті, у даному випадку вдалось зменшити кількість ітерацій з шести до чотирьох, перша з яких – це звертання до цих блоків. Відповідно, схема добування кореня стала меншою на три суматори та три мультиплексори

Недоліком модифікованого алгоритму є те, що блоки постійної пам’яті повинні мати 2k-розрядні адресні входи. Через це вони мають значний об’єм при великому k.

Проте, цей алгоритм доцільно використовувати в сучасних ПЛІС при k ≤ 6. Так, при k= 3 для n = 24-розрядних даних параметри блоку квадратного кореня наведені в табл.5.1., тобто з застосуванням цього алгоритму параметри блоку квадратного кореня покращуються.

У генераторі віртуальних модулів квадратного кореня організовано ввід таких параметрів, як розрядність вхідних та вихідних n даних, розрядність 2k адрес блоків постійної пам’яті, наявність вхідного та вихідного регістрів, побудова повністю конвеєризованої чи частково конвеєризованої схеми, тобто з n - k або з ](n - k)/2[ ступенями конвеєра. При цьому користувачу даються оцінки апаратних витрат модуля та максимальної тактової частоти.

Згенерований модуль SQRT призначений для розрахунку квадратного кореня для цілого аргументу. Тобто, при вхідній розрядності 2n старші n розрядів результату представляють цілу частину числа, а решта розрядів – дробову частину.

Розрядність вхідних ('Вхідна розрядність') та вихідних ('Вихідна розрядність') даних можуть бути будь-які цілі числа більші за чотири

Коли не вибрано кнопку 'Вхід синхросигналу' , то модуль SQRT генерується як комбінаційна схема без регістрів. Коли вона обрана, то до цієї схеми додається набір регістрів.

При виборі перемикача 'Регістри на вході та виході', два регістра будуть встановлені на вході і виході модуля. При виборі перемикача 'Кожні 2 ступеня з регістром' додаткові конвеєрні регістри встановлюються між кожними двома ступенями структури модуля. У разі вибору кнопки 'Кожний ступінь з регістром' максимальне число конвеєрних регістрів встановлюється у модулі. Очевидно, що конвеєрні регістри забезпечують збільшення максимальної тактової частоти модуля за рахунок збільшення латентної затримки.

Вибравши кнопку 'Дозвіл синхросигналу' можна додати до схеми модуля вхід CE, який контролює тактовий сигнал. Цей вхід використовують для уповільнення роботи модуля.

Структура модуля SQRT відрізняється тим, що від однієї до п'яти перших ітерацій алгоритму обчислення кореня реалізовані з використанням логічних таблиць LUT. Розрядність адреси ЛТ вибирається у вікні 'Розрядність адреси LUT' . Максимальна розрядність адреси дорівнює десяти. Слід відмітити, що сучасні ПЛІС фірм Xilinx, і Altera побудовані на 6-розрядних ЛТ.

При виборі кнопки 'Показати характеристики' виводяться наближені характеристики модуля SQRT для обраних вхідних параметрів. Це об’єм апаратних витрат, латентна затримка в тактах і максимальна тактова частота для ПЛІС типу Xilinx Spartan-6. Ці характеристики наведені тільки для довідки. Більш точні характеристики можуть бути отримані тільки після конфігурування цього модуля в конкретній ПЛІС.

Слід відмітити, що, коли вибрано 10-розрядні ЛТ, а синтез схеми спрямований на використання блоків пам’яті BlockRAM то реальні апаратні витрати є набагато меншими, ніж тій, що приводяться для оцінки.

При виборі кнопки 'Модуль вивести на екран' на екран виводиться VHDL-код згенерованого модуля. Текст цього коду може бути переміщений в середовище користувача за допомогою екранних функцій Select, Copy і Paste.

Згенеровані віртуальні модулі можуть бути зконфігуровані у ПЛІС усіх компаній-виробників та більшості типів. У таблиці 1 наведені середні параметри модуля SQRT, які зконфігуровані для деякий ПЛІС фірми Xilinx. Наведені параметри отримані для 16-розрядних вхідних і вихідних даних без особливих настроювань файлу обмежень для синтезу, розміщення та трасування.

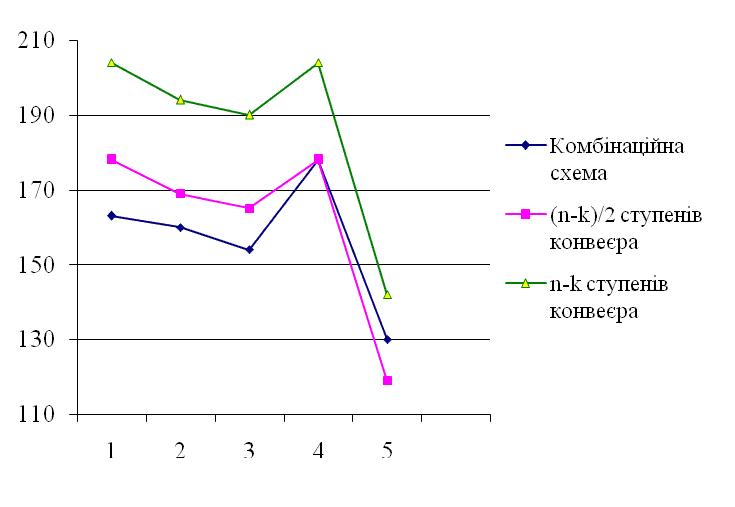

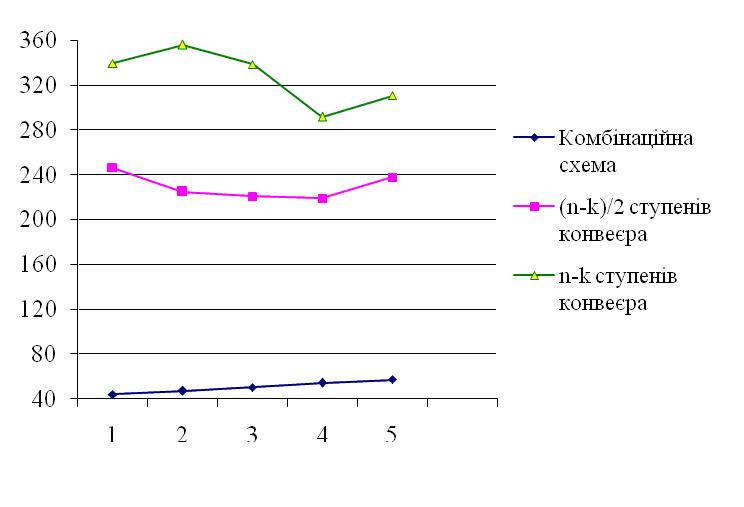

Після синтезу та розміщення модулів блоку квадратного кореня у ПЛІС Xilinx Spartan-6 було одержано ряд характеристик апаратних витрат (рис.2) у кількості ЛТ та максимальної тактової частоти, МГц (рис.3) для різних значень k при вхідній розрядності 24 та розрядності результату n = 12. Розглядались модулі у вигляді комбінаційної схеми, повністю конвеєризовані та частково конвеєризовані модулі.

Таблиця 1. Параметри модуля SQRT

| Параметр | Конвеєризація | Virtex-4 | Spartan-6 | Virtex-7 |

| Апаратні витрати, ЛТ | Без конвеєризації | 281 | 277 | 309 |

| РАпаратні витрати, ЛТ | Половинна конвеєризація | 269 | 214 | 238 |

| Апаратні витрати, ЛТ | Повна конвеєризація | 292 | 275 | 302 |

| Тактова частота, МГц | Без конвеєризації | 35 | 32 | 62 |

| Тактова частота, МГц | Половинна конвеєризація | 196 | 174 | 333 |

| Тактова частота, МГц | Повна конвеєризація | 298 | 271 | 552 |

Рис.2. Апаратні витрати блоку √x x в залежності від k

Рис.3 Максимальна тактова частота блоку √x в залежності від k