Темы бакалаврских и дипломных работ.

Блоки операций с плавающей запятой

Назначение.

Блоки операций с плавающей запятой предназначены для реализации в ПЛИС

вычислений с повышенной точностью и /или снятия проблемы масштабирования

промежуточных результатов. Представление данных последовательными кодами и

последовательно- параллельные вычисления в этих блоках позволяют

- минимизировать аппаратурные затраты на реализацию функций и за счет этого дать возможность реализовать в ПЛИС достаточно сложные алгоритмы с полным распараллеливанием (отображение графа алгоритма в структуру как 1:1);

- минимизировать длительность тактового интервала до предельно возможной для ПЛИС за счет конвейеризации и минимизации критического пути в логических схемах;

- свести период реализации всех операций (в том числе операций вычисления элементарных функций) к одному или двум значениям, что упрощает планирование сложных конвейерных вычислений;

- эффективнее эксплуатировать память на задержках LUT ПЛИС серии Xilinx Virtex.

Представление данных.

Данные представляются числами с фиксированной запятой в дополнительном коде и числами с плавающей запятой. Точность представления мантиссы и числа с фиксированной запятой задается как в таблице 1:

Таблица 1.

| Число разрядов n | Название | Префикс |

| 8 | байтовая | B |

| 16 | Полуслово | H |

| 24 | Одинарная | S |

| 32 | расширенная | E |

Данные с фиксированной запятой предназначены для интерфейса с другими

вычислительными блоками, которые могут быть применены в проекте, в котором применяются данные блоки. Они представляются параллельными n-разрядными кодами.

Данные с фиксированной запятой представляются как целые числа:

Данные с плавающей запятой имеют n-1 — разрядную мантису в прямом коде с неявно заданной старшей единицей, знак мантиссы и 8-разрядный абсолютный порядок без смещения:

| Знак | Порядок | Мантисса | ||||||

| n+7 | n+6 | n+5 | … | n-1 | n-2 | n-3 | … | 0 |

В формате с плавающей запятой должны быть закодированы следующие

исключительные сосотояния:

- Плюс-минус ноль = порядок и мантисса — нулевые, кроме знака;

- Плюс-минус бесконечность — порядок = 255, мантисса -нулевая , кроме знака;

- Не-число (NAN) — порядок = 255, мантисса- все 1.

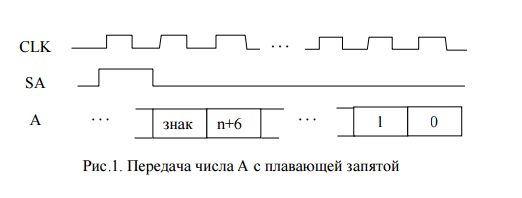

Данные с плавающей запятой представляются и передаются последовательным кодом

старшими разрядами вперед. Начало числа сопровождается импульсом SA, как на рисунке 1.

Интерфейс

Блоки должны иметь унифицированный интерфейс.

Кроме того, блоки, выполняющие преобразование типов из/ в целое число имеют

параллельные входы/ выходы n-разрядных шин целых чисел, соответственно.

Если блок обрабатывает 2 числа DA и DB, и они поступают неодновременно, то начало выполнения операции совпадает с поступлением последнего операнда (уточняется в процессе выполнения проекта).

Если блок управляется дополнительными сигналами, напр. SIGN, то этот сигнал

записывается блоком в период поступления знакового разряда числа.

Перечень операций представлен в таблице 3.

Таблица 3.

| Cимвол | Операнды | Признаки | Функция |

| ADDSUB | DA,DB | GE,ZR,INF | Сложение если SGN=0,вычитание DA-DB если SGN=1 |

| MUL | DA,DB | GE,ZR,INF | Умножение |

| DIV | DA,DB | GE,ZR,INF,NAN | Деление |

| ABS | DI | Абсолютное значение | |

| ACCUM | DI | GE,ZR,INF | Накопление в аккумуляторе |

| SQRT | DI | ZR,NAN | Квадратный корень |

| SINPI | DI | GE,ZR | Синус аргумента, умноженного на Пи |

| ATAN | DA,DB | GE,ZR,NAN | Арктангенс от DA/DB |

| MOD | DA,DB | GE,ZR,INF | Модуль комплексного числа: SQRT(DA*DA+DB*DB) |

| MUL2CONST | DI | GE,ZR,INF | Умножить на константу, заданную как Generic |

| ADD2CONST | DI | GE,ZR,INF | Добавить константу, заданную как Generic |

| TANPI | DI | GE,ZR,INF | Тангенс аргумента, умноженного на Пи |

| LOG2 | DI | ZR,NAN | Логарифм по основанию 2 |

| EXP2 | DI | GE,ZR,INF | 2 в степени аргумента |

| REAL2INT | DI | GE,ZR,INF | преобразование в целое |

| INT2REAL | DI | GE,ZR | преобразование из целого в реальное |

| В2H,H2S,S2E, E2S,S2H,H2B, B2S,H2E,S2B, E2H |

DI | Преобразование точности представления аргумента, например, В2Н – из байтовой мантиссы в 16-разрядную мантиссу |