Что такое FPGA?

Анатолий Сергиенко

Программируемые логические интегральные схемы (ПЛИС) появились полтора десятилетия назад как альтернатива программируемым логическим матрицам (ПЛМ). От последних ПЛИС отличаются как по архитектуре, так и по технологии изготовления.

ПЛМ представляет собой матрицу многовходовых (несколько десятков входов) логических элементов с триггерами, в которых перемычками программируются конституенты единиц дизъюнктивных нормальных форм функций этих элементов. Вначале перемычки выполнялись в виде пережигаемых тонких проводничков. Теперь перемычки выполняются в виде МОП-транзистора с плавающим затвором, как в электрически перепрограммируемом ПЗУ, т.е. ПЛМ изготовляются по технологии флэш-памяти. Большие ПЛМ (CPLD) отличаются только тем, что несколько ПЛМ собраны на одном кристалле и объединены программируемым полем связей.

ПЛИС представляет собой матрицу маловходовых (от двух до пяти входов) логических элементов, триггеров, отрезков линий связи, соединяемых перемычками из полевых транзисторов. Судя по английскому названию — Field Programmable Gate Array (FPGA) — ПЛИС программируются изменением уровня электрического поля (field) в затворах этих транзисторов. В отличие, например, от LPGA — Laser Programmable Gate Array. Затворы всех «программирующих» полевых транзисторов подключены к выходам триггеров одного длинного сдвигового регистра, который заполняется при программировании ПЛИС. Некоторые из участков этого регистра могут также выполнять роль ячеек ПЗУ.

Прошивка обычно хранится в ПЗУ, стоящем рядом с ПЛИС и после включения питания или по сигналу сброса она автоматически переписывается в программирующий сдвиговый регистр ПЛИС. Этот процесс называется конфигурированием ПЛИС. Так как основу ПЛИС составляют триггеры, хранящие прошивку, то ПЛИС изготавливаются по технологии микросхем статического ОЗУ.

По сравнению с CPLD, ПЛИС выигрывают

- во-первых, в неограниченном количестве перепрограммирований,

- во-вторых, в логической емкости, в том числе в удельной емкости вентилей на цент,

- в-третьих, в малом энергопотреблении.

Как правило, ПЛИС имеют на два — три порядка большую емкость в числе эквивалентных логических вентилей, чем CPLD и также как статическое ОЗУ, почти не потребляют энергии при отсутствии переключений. Кроме того, у ПЛИС на порядок выше надежность (ниже интенсивность отказов), чем у CPLD.

К недостаткам относят необходимость внешнего ПЗУ прошивки, генератора синхросерии. Но 8-выводовое ПЗУ занимает на плате значительно меньше места, чем сама ПЛИС с многими сотнями выводов. То же касается генератора синхросерии.

Много сомнений у пользователей возникает с защитой проекта от копирования. Действительно, прошивка ПЛИС хранится во внешнем ПЗУ, содержимое которого просто копируется. Но изменить или расшифровать прошивку, например, для скрытия авторства или восстановления схемы, практически невозможно, так как семантика битов в файле прошивки — секрет фирмы, а неосторожное изменение ее может вывести ПЛИС из строя. Если требуется защита, то загрузку программы выполняют с помощью внешней CPLD, автомат в которой обеспечивает защиту проекта. В ПЛИС новых поколений предусматривается шифрование прошивки, например, с помощью встроенного шифрователя DES с обеспечением сохранения ключа с помощью батарейки.

Архитектура ПЛИС фирмы Xilinx.

Фирма Xilinx принадлежит к числу родоначальников ПЛИС и самых крупных их производителей. Ниже рассматривается краткое описание архитектурных особенностей ПЛИС серии Virtex выпускаемой этой фирмой. Эти особенности наследуются в новых сериях ПЛИС, а также в серии Spartan, микросхемы которой призваны заменить заказные СБИС в мало- и среднесерийном производстве изделий электроники. Кроме того, принципы функционирования структурных элементов ПЛИС этой серии узнаваемы в архитектурах ПЛИС других фирм-производителей, таких как, Altera, Actel, Atmel.

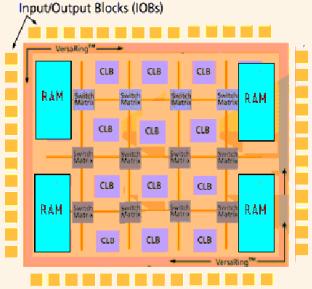

Топология ПЛИС.

На площади кристалла ПЛИС размещены матрица конфигурируемых логических блоков (КЛБ или CLB), матрица отрезков линий межсоединений, покрытых матрицами из полевых транзисторов — перемычек. По краям кристалла размешены блоки настраиваемых ОЗУ — BlockRAM. По периметру кристалла размещены блоки ввода-вывода сигналов (IOBs), а также периферийный канал линий межсоединений, называемый Versaring, предназначеный для соединения КЛБ с произвольным IOB линией связи с малой задержкой.

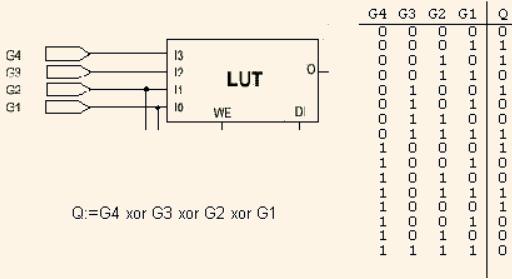

Логическая таблица.

Роль основного логического элемента в ПЛИС играет логическая таблица (ЛТ) или look-up table (LUT), представляющая собой однобитное ОЗУ на 16 ячеек. В ЛТ по адресу G3,G2,G1,G0 записана единица, если код адреса представляет собой конституенту единицы заданной четырехвходовой логической функции. Например, если по адресу 1,1,1,1 записана единица, а по остальным адресам — ноль, то ЛТ реализует четырехвходовую функцию И. На рис. показан пример кодирования функции Исключающее ИЛИ на четыре входа.

Триггеры ЛТ входят в состав программирующего сдвигового регистра и их начальное состояние заполняется в период конфигурирования ПЛИС.

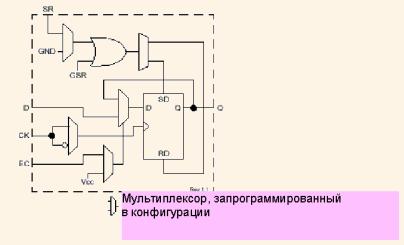

Триггер.

В ПЛИС используются программируемые D-триггеры. При конфигурировании можно задать такие режимы работы триггера, как триггер с начальным сбросом (R) или начальной установкой (S), с записью по фронту или спаду синхросерии, с разрешением или без разрешения записи.

После окончания конфигурирования ПЛИС выдает сигнал общего сброса GSR, который устанавливает все триггеры в 0 или 1.

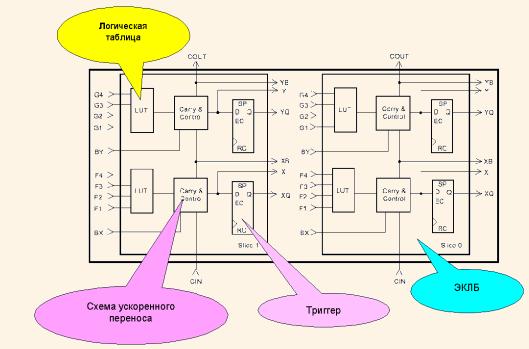

Структура КЛБ.

В базовой серии ПЛИС XC4000 фирмы Xilinx основной единицей оборудования считается КЛБ, состоящий из двух триггеров и двух ЛТ. В новых сериях ПЛИС количество триггеров и ЛТ увеличилось вдвое и вчетверо. Чтобы оставить для всех серий одну и ту же единицу оборудования, условились называть КЛБ из двух триггеров и двух ЛТ эквивалентным КЛБ (ЭКЛБ) или CLB slice. Таким образом, КЛБ серии Virtex состоит из двух ЭКЛБ, а серии VirtexII — из четырех ЭКЛБ .

Схемы для ускорения арифметических операций.

В ЭКЛБ две ЛТ и два триггера соединены вместе через схему ускоренного переноса и два однобитных полусумматора. Эти схемы позволяют эффективно реализовать многоразрядные параллельные сумматоры, а на их основе — всевозможные счетчики и АЛУ.

Для минимизации оборудования и ускорения вычисления операции умножения используется дополнительная схема поразрядного произведения.

Следует добавить, что в новой серии VirtexII аппаратно реализованы умножители 18 на 18 разрядов.

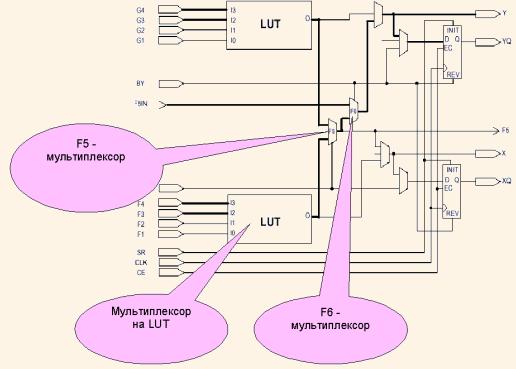

Мультиплексоры в ПЛИС.

Большую долю оборудования в ВС занимают мультиплексоры. С помощью ЛТ можно реализовать двухвходовый мультиплексор. Для эффективной реализации 4-х и более — входовых мультиплексоров в КЛБ имеются схемы мультиплексоров F5 и F6, которые играют роль верхних уровней древовидного мультиплексора. Также они используются для построения функции 5-входовой (F5) и 6-входовой (F6) логики.

Шины с тремя состояниями.

Применение шин с тремя состояниями — типичное схемное решение вычислительных устройств, реализованных на плате. Благодаря такому решению, легко достигается многомодульность и наращиваемость системы, низкие аппаратурные затраты и малые задержки в системе межсоединений. Внутри заказных СБИС редко применяются шины с тремя состояниями из-за технологических трудностей их безотказной реализации, а также увеличенной задержки на их переключение.

Несмотря на это, в ПЛИС фирмы Xilinx всё-таки широко применяются шины с тремя состояниями, хотя это существенно повышает их себестоимость. Зато, во-первых, проще выполнить переход от проекта схемы на плате к проекту системы на кристалле. Во-вторых, ВУ с общими шинами, к которым подключено несколько десятков модулей, имеет аппаратные затраты в несколько раз меньше, чем такое же ВУ, в котором шины заменены на эквивалентную схему из системы мультиплексоров. В-третьих, с помощью общих шин можно эффективно реализовать встроенное распределенное ОЗУ, о котором пойдет речь ниже.

Для реализации общей шины каждый КЛБ имеет два буфера с тремя состояниями BUFT , которые через транзисторы-перемычки могут подключаться к общим шинам, проходящим вдоль всего кристалла. В обычных шинах третье состояние характеризуется уровнем, находящимся между уровнями логической 1 и логического 0. Но если такую шину реализовать внутри микросхемы, то в случае, когда все тристабильные буферы будут в третьем (закрытом) состоянии, их выходные транзисторы будут полуоткрытыми и могут выйти из строя. Для исключения такого электрического режима в ПЛИС общая шина нагружена на концах специальной триггерной схемой — Weak Keeper , которая выводит уровень шины или к уровню H, или к уровню L (слабые 1 или 0), если все буферы закрыты.

Неправильное функционирование общей шины, когда несколько источников с разными уровнями подключаются к шине, может вывести ПЛИС из строя. САПР ПЛИС тщательно проверяет, чтобы спроектированная общая шина функционировала правильно. Поэтому не рекомендуется ручное редактирование файла прошивки, так как случайная ошибка в коде может привести к неправильной работе общей шины и порче ПЛИС.

ОЗУ в ПЛИС.

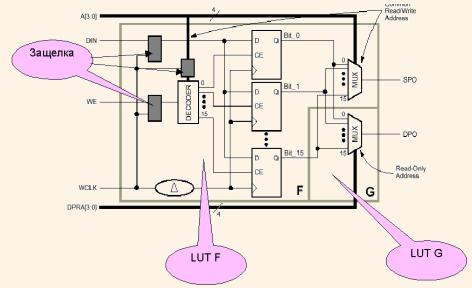

Для реализации в ПЛИС модулей ОЗУ предусмотрено две возможности. Первую возможность предоставляет каждая ЛТ, которая может быть сконфигурирована как 16-битовое синхронное ОЗУ. Две соседних ЛТ могут быть сконфигурированы как 16-битовое двухпортовое ОЗУ с записью и чтением по одному адресу и чтением по другому адресу, как показано на рис. При этом для реализации синхронного режима записи входной бит данного, сигнал записи и адрес запоминаются в триггерах — защелках, а для чтения по второму адресу из блока второй ЛТ используется только мультиплексор чтения.

Для наращивания емкости памяти выходы нескольких КЛБ с модулями ОЗУ через тристабильные буферы подключаются к общим шинам. При этом требуется дополнительное оборудование только для построения схемы дешифрации адреса, которая выдает сигналы выборки той или иной ЛТ для записи, а также того или другого тристабильного буфера для чтения. Такое ОЗУ распределено по площади кристалла и поэтому названо Distributed RAM.

Если ЛТ запрограммировать как примитив SRL16, то из ее триггеров будет реализован 16-разрядный сдвиговый регистр с однобитовым входом и программируемым номером выходного разряда, т.е. память FIFO регулируемой длины.

Вторую возможность предоставляют отдельные блоки памяти BlockRAM. В ПЛИС серии Virtex они могут быть сконфигурированы как ОЗУ объемом 256 16-разрядных слов, 512 8-разрядных слов, и т.д. Эта память может быть запрограммирована как однопортовая или как полностью двухпортовая память. Начальное состояние этой памяти задается при ее конфигурировании, поэтому она может быть использована также как ПЗУ.

Блоки ввода-вывода сигналов.

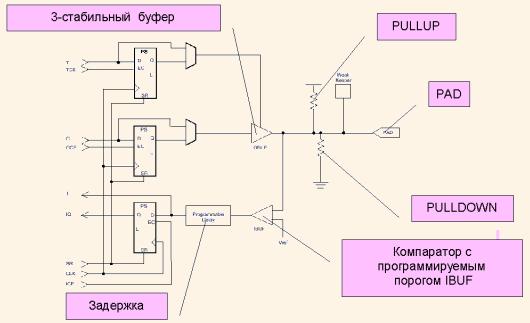

ПЛИС находят широкое применение благодаря тому, что их можно включать в большинство проектов вычислительных устройств и ими можно заменять большое количество старых микросхем. Предпосылкой этому служит большое число блоков ввода-вывода сигналов IOB, настраиваемых под различные стандарты электрического соединения входов микросхем. На рис. показана структура одного IOB.

Сигнальный вывод ПЛИС получил название PAD. С помощью настройки к нему можно подключать внутренний нагрузочный резистор PULLUP или резистор PULLDOWN, соединенные с шиной питания или шиной земли, соответственно. Эти резисторы обеспечивают режим выхода с открытым коллектором (стоком) для систем с различными уровнями логики. Входной сигнал с PAD поступает на компаратор IBUF, порог срабатывания которого программируется под уровни ТТЛ, КМОП, шины PCI и многие другие, а также может регулироваться установкой подаваемого снаружи напряжения. Для обеспечения временного сдвига сигнала относительно фронта синхросерии, обеспечивающего надежный прием сигнала во внутренние триггеры, в цепь входного сигнала может включаться специальная схема задержки.

Выходной сигнал в IOB формируется в тристабильном буфере OBUFT, причем его уровень максимального тока программируется ступенями и может достигать 20 мА. Для обеспечения быстродействующего ввода-вывода передаваемые и принимаемые биты данных, а также сигнал управления тристабильным буфером могут запоминаться в триггерах.

В новых сериях ПЛИС предусмотрена настройка входного и выходного импеданса PADа, а также бифазное функционирование пар PADов для достижения помехоустойчивой высокоскоростной передачи данных.

При диагностике и отладке, в одном из режимов конфигурирования ПЛИС может быть переключена в режим пограничного сканирования (Boundary Scan). В этом режиме все IOB соединяются в цепочку одного длинного регистра сдвига. Путем стандартного внешнего управления этим регистром сдвига через интерфейс JTAG можно считывать состояния выводов, подавать тестовые сигналы, конфигурировать ПЛИС.

В период конфигурирования ПЛИС для того, чтобы подключаемые к ней устройства не функционировали неопределенным образом, выходы IOB отключаются и на них обычно выставляется уровень H слабой единицы (Weak Keeper).

Система синхронизации.

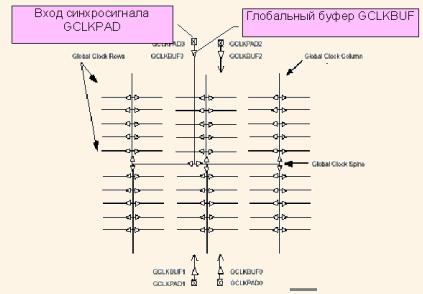

Одним из принципов разработки проектов для ПЛИС является принцип однотактной синхронизации, согласно которому все триггеры в блоке срабатывают одновременно по одному сигналу синхросерии. Для его реализации в ПЛИС синхросигналы распространяются по быстродействующей древоообразной сети, которая обеспечивает почти одновременный приход фронта синхроимпульса на синхровходы всех триггеров.

Для надежного функционирования ПЛИС синхросигнал должен подаваться через вывод GCLKPAD и попадать в сеть синхросерии через буфер GCLKBUF. В ПЛИС предусмотрено 4 вывода GCLKPAD, размещенных на противоположных сторонах ее корпуса. Синхросигнал может вырабатываться и внутри ПЛИС, но в этом случае его следует завести в сеть синхросерии через глобальный буфер BUFG.

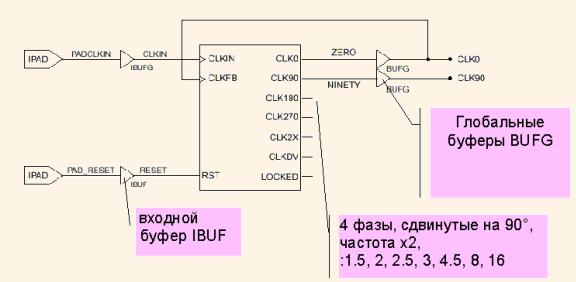

С помощью спроектированного синхронного автомата, сконфигурированного в ПЛИС, можно изменять частоту и фазу синхросерии. Но в этом случае ее временные параметры будут недостаточно стабильными и поэтому такой подход обычно не применяется. Для надежного регулирования частоты синхросерии в ПЛИС включают делители частоты синхросерии с автоподстройкой — блоки CLKDLL. На рис. показана типичная схема его включения. Блок CLKDLL обеспечивает умножение частоты синхросерии в 2 раза, сдвиг ее фазы на 90, 180 и 270 градусов, деление на 1.5, 2, 2.5, 3, 4.5, 8 и 16.

Конфигурирование ПЛИС.

Для конфигурирования ПЛИС в ней предусмотрены входы задания режима M2, M1, M0, вывод синхросерии программирования CCLK, вход последовательности конфигурации PROGRAM, выход флага окончания конфигурирования DONE и выводы порта JTAG. В зависимости от установленного режима можно загружать прошивку ПЛИС через однобитовый вход PROGRAM, порт JTAG или 8-разрядную шину D c использованием для управления выводов WRITE и BUSY.

Конфигурирование через однобитовый вход длится до нескольких десятков секунд. Это стандартный способ конфигурирования и для него не требуется дополнительного оборудования, кроме ПЗУ прошивки с однобитовым выходом.

Для реализации конфигурирования через шину D необходимо дополнительное внешнее устройство (автомат или микроконтроллер), управляющее записью и выдающее последовательность адресов чтения на входы байтового ПЗУ. Зато оно происходит значительно быстрее — практически с максимальным темпом чтения из ПЗУ.

Разработка систем на кристалле (СНК) — это устойчивая современная тенденция. И программирование ПЛИС для СНК — один из главных этапов такой разработки. Выпуск ПЛИС новых поколений, например, Xilinx VirtexPro, направлен на поддержку развития СНК. Разработка СНК без применения языка VHDL или Verilog практически невозможна.