Стили написания программ на VHDL

( http://www.electronics-eetimes.com/sites/default/files/documents/whitepapers/1-edn-pdfarticles/download-pdf-1606-feat-e2v.pdf )

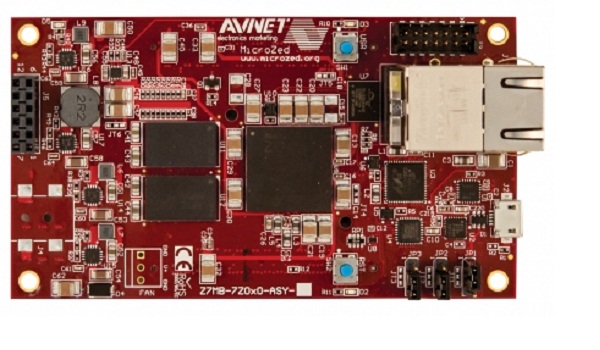

Стили написания программ на VHDL исследовал Адам Тейлор, главный инженер фирмы Electrical Systems at E2V, который ранее был руководителем разработок в ведущей европейской компании Astrium, которая занималась разработкой космических телекоммуникационных процессоров на базе заказных СБИС и ПЛИС Virtex 5 QV. В Интернете он известен как автор серии заметок и соответствующей книги MicroZed Chronicles об опыте программирования платы Avnet MicroZed на базе ПЛИС Xilinx Zynq (на фото).

Есть несколько стилей написания VHDL-кодов. Основное отличие между ними в том, как выделяются ключевые слова.

Согласно первому стилю, весь текст состоит из строчных букв.

Согласно второму стилю, ключевые слова набирают строчными буквами, а остальные, включая названия типов, библиотек — большими, как это сделано в справочнике по VHDL (VHDL Language Reference Manual).

Согласно третьему стилю — наоборот — ключевые слова набирают большими буквами, а остальные — строчными.

Главным аргументом того, что ключевые слова следует выделять высотой букв является то, что это помогает инженерам и тестировщикам их быстро находить и распознавать как синтаксические единицы.

Но в наше время распространены редакторы текстов программ, распознающие синтаксис и подсвечивающие цветом ключевые слова. Если в таком редакторе читать VHDL-тексты, написанные тремя указанными стилями, то не удается отдать предпочтение одному из этих стилей. Итак, соблюдение определенного стиля теряет смысл и не является обязательным.

Хотя такие новые редакторы довольно эффективны, не следует забывать, что некоторые пользователи не различают цветов, а некоторые из членов команды разработчиков пользуются обычным редактором или читают текст с черно-белого листа.

Многие компании внедряют свой собственный стиль кодирования. Такой стиль принимает во внимание следующие особенности задания сигналов.

— Согласование имен синхросигналов, например, имя сигнала включает значение его частоты: clk_40MHz.

— Согласование имен сигналов начального установления (активная единица или активный ноль) и их положение относительно синхросигнала (близкое положение сигнала асинхронного сброса к фронту синхросигнала может привести к попаданию в метастабильное состояние).

— Согласование имен сигналов, например, сигналов разрешения, которые имеют нулевой активный уровень. Такое имя часто имеет суффикс типа _n или _z. Например, RAM_CS_n.

— Задается конкретное множество библиотек, которые разрешено использовать. Например, в современном проекте разрешается библиотека std_logic_1164, как обязательная, numeric_std, как библиотека арифметических функций и не разрешается аналогичная библиотека std_arith, как устаревшая. А библиотеки text_io, math_real разрешены только для стендов для испытаний.

— Регламентируется использование типа std_logic и std_ulogic для определенного рода сигналов и портов (std_logic — это тип std_ulogис, для которого определена функция решения конфликта в случае, когда сигналу выполняется присваивание в нескольких параллельных операторах).

— Определяются разрешенные режимы портов. Многие компании требуют использования только режимов in, out и inout (только для двунаправленных шин) и запрещают использование buffer. Также большинство компаний регламентируют типы портов только std_logic или std_logic_vector чтобы проще стыковать модули от разных разработчиков, особенно в большом коллективе.

— Как правило, если проект касается критического применения, то регламентируется использование переменных в процессах.