Вычислительный модуль 16-разрядного RISC-микропроцессора

А. М. Сергиенко

1. Назначение и название RISC-микропроцессора.

Учебный RISC-микропроцессор RІSC_ST (student — сокращенно — ST) предназначен для изучения основ построения и проектирования RISC-микропроцессоров с помощью VHDL. Он также предназначен для экспериментальных целей, для разработки и проверки новых методов проектирования ВС на СНК. По своим техническим характеристикам и, прежде всего, по архитектуре он соответствует процессорам для реализации в СНК систем реального времени. Проект процессора ориентирован на реализацию в ПЛИС фирми Xіlіnx, но может быть также реализован в ПЛИС других фирм, а также заказных СБИС.

Под архитектурой процессора понимают набор основных сведений, необходимых для разработки этого процессора и его использования. Как правило, эти сведения включают в себя

- структуру процессора,

- информацию о системе команд, системе прерываний, адресном пространстве и порядке доступа к памяти,

- состав и схему подключения периферийного оборудования,

- организацию виртуальной адресации и кэш-памяти,

- латентные задержки выполнения операций и доступа к памяти,

- множество команд, которые могут выполняться параллельно,

- механизмы защиты доступа к ресурсам, изменению контекста, многопотоковой обработки и т.д.

Архитектура RІSC_ST характерна тем, что она включает все основные особенности RISC-процессоров, такие как простой формат команд, конвейеризация, выполнение команд во время отработки команды перехода, регистровая память. Для работы в реальном времени процессор имеет повышенное быстродействие не только за счет однотактового выполнения команд, но и благодаря аппаратно реализованному стэку и быстродействующей системе прерываний.

RІSC_ ST-процессор имеет 16-разрядные данные и команды. Такой разрядности достаточно для реализации большого множества задач, которые решаются в СНК.

Детально разработка этого процессора описана в книге: Сергиенко А.М. VHDL для проектирования вычислительных устройств. -Киев: ДиаСофт, -2003, -208 с.

Попытка его модификации с разработкой ассемблера подробно изложена на форуме http://electronix.ru/forum/index.php?showtopic=60367&st=30

2. Система команд.

В процессоре множество команд разбито на четыре типа. Типы и поля команд указаны в таблице 1, а перечень команд, их кодирование и краткое описание показаны в таблице 2. В поле F устанавливается флаг разрешения прерываний, поле СОР обозначает код операции, в полях RD и RS показаны адреса регистров, поле Func кодирует тип перехода или арифметической операции, поля Imm и Dіsp задают 8-разрядный непосредственный операнд и сдвиг адреса, соответственно, а поле Cond — условие перехода.

Таблица 1. Типы и поля команд

| Тип команды | Разряды команды | ||||

| 15 | 14-12 | 11-8 | 7-4 | 3-0 | |

| RR | F | COP | RD | RS | Func |

| RI | F | COP | RD | Imm | |

| BRA | F | COP | Cond | Disp | |

| JMP | F | COP | Cond | RS | Func |

Таблица 2. Перечень команд, их кодирование и краткое описание

| Команда | Разряды команды | Описание | ||||

| Имя | Тип | 14-12 | 11-8 | 7-4 | 3-0 | |

| NOP | JMP | 000 | 0000 | 0000 | 0000 | Нет операции | CALL | JMP | 000 | Cond | RS | 0001 | Вызов подпрограммы по {RS} |

| RET | JMP | 000 | Cond | — | 0010 | Возврат из подпрограммы |

| RETI | JMP | 000 | Cond | — | 0100 | Возврат из подпрограммы прерываний |

| LJMP | JMP | 000 | Cond | RS | 1000 | Условный переход по {RS} |

| BRA | BRA | 001 | Cond | Disp | Условный переход по адресу {PC}+Disp | |

| LD | RR | 010 | RD | RS | Imm4 | Загрузка в регистр RD данного по адресу {RS}+Imm4 | SD | RR | 011 | RD | RS | Imm4 | Сохранение данного с RD по адресу {RS}+Imm4 |

| LL | RI | 100 | RD | Imm | Загрузка Imm в младший байт регистра RD | |

| LH | RI | 101 | RD | Imm | Загрузка Imm в старший байт регистра RD | ADDI | RR | 110 | RD | RS | Imm4 | Запись RS+Imm4 в RD | ALU | RR | 111 | RD | RS | Func | Запись RS (Func) RD в RD |

Регистровые команды RR выполняют разные действия над содержимым регистров RD и RS с записью результата в регистр RD (команды ALU и ADDI), а также пересылку данного между регистром RD и ячейкой памяти данных с адресом из регистра RS (команды загрузки LD и сохранения SD). Команда ALU выполняет функцию логического И — AND, исключительного ИЛИ — XOR, логического и арифметического сдвига вправо на один разряд — SRL, SRA, сложения и вычитания — ADD, SUB, сложения и вычитания с переносом — ADDC, SUBC.

В таблице 3 представлено кодирование функций этой команды. Команда ADDI прибавляет к содержимому регистра RS четырехразрядную непосредственную константу Imm4. При обращении к памяти данных в командах LD и SD к адресу данного прибавляется непосредственный прирост Imm4.

Таблица 3. Кодирование функций команды ALU.

| Имя | Func | Описание |

| AND | 0000 | RD and RS -> RD |

| XOR | 0001 | RD xor RS -> RD |

| SRL | 0010 | ‘0’ & RS(15..1) -> RD |

| SRA | 0011 | RS(15) & RS(15..1) -> RD |

| ADD | 1000 | RD + RS -> RD |

| SUB | 1001 | RD — RS -> RD |

| ADDC | 1010 | RD + RS +C -> RD |

| SUBC | 1011 | RD — RS — C -> RD |

По командам JMP выполняется вызов подпрограммы — CALL, возвращение из нее — RET, возвращение из подпрограммы прерываний — RETI и условный переход по абсолютному адресу — LJMP. При этом адрес перехода берется из регистра RS. Условия перехода такие же, как и в команде BRA.

Все непосредственные операнды команд, кроме Imm, представляют собой целые числа со знаком в дополняющем коде.

Регистровые команды с непосредственным операндом RI выполняют загрузку в старший байт RD или младший байт RD непосредственного 8-разрядного операнда (команды LH и LL, соответственно).

Команда BRA выполняет переход относительно состояния регистра адреса со сдвигом Disp по условию Cond. В таблице 4. показаны возможные условия перехода.

Таблица 4. Возможные условия перехода.

| Имя | Cond | Описание |

| JUMP | 0001 | Безусловный переход |

| NOP | 0000 | Нет перехода |

| EQ | 0011 | Результат Y=0 |

| NEQ | 0010 | Результат Y≠0 |

| LT | 0101 | Результат Y<0 |

| GE | 0100 | Результат Y>0 |

| LE | 0111 | Результат Y<0 |

| GT | 0110 | Результат Y>0 |

| CY | 1001 | Перенос |

Система команд процессора предоставляет достаточно возможностей для решения широкого круга задач. Много команд, которые не указаны в табл. 2-4, можно рассматривать как особый случай кодирования этих команд или программировать их цепочкой команд. Например, команда сдвига влево SLL RD; — это команда ADD RD,RD; команда пересылки MOV RD,RS; — это команда ADDI RD,RS,#0; команда установления в нуль регистра — это XOR RD,RD. Загрузка любой константы С = 256*СH+CL выполняется двумя командами: LH RD, CH; LL RD, CL.

Как правило, в нулевом регистре RISC-процессора сохраняется нуль. Тогда команда инверсии NEG RD; — вычисляется как SUB RD,0; а команда порозрядного инвертирования NOT RD; вычисляется парой команд: ADDI 1, 0, #-1; XOR RD, 1;.

Более сложные операции, такие как умножение, деление, вычисляются по подпрограммам. Кроме того, когда в зависимости от применения процессора, сложные вычисления требуют повышенного быстродействия, эти вычисления могут быть реализованы в периферийных устройствах, специально разработаных для этого.

Архитектура RISC_ST предполагает добавление других команд, функций ALU, условий перехода для увеличения функциональности, быстродействия, а также для учебных и экспериментальных целей.

3. Пространство адресов.

Микропроцессоры для встраивания в аппаратуру должны иметь повышенную надежность функционирования. Согласно одному из правил обеспечения надежности, не допускается изменение программы в процессе ее выполнения. Проще всего это достигается, когда программа сохраняется в ПЗУ или ОЗУ, к которому нет прямого программного доступа. Кроме того, когда команды и данные сохраняются в отдельных блоках памяти, к ним можно реализовать параллельный доступ. Таким образом, процессор RISC_ST должен иметь отдельный блок ОЗУ программ PRAM и блок ОЗУ данных DRAM. Разрядность процессора обеспечивает адресацию до 65К слов PRAM и до 65К слов DRAM. Можно увеличить размер DRAM, добавляя страничную адресацию.

Основная программа размещается в адресном пространстве PRAM, начиная с адреса INI_ADDR. По сигналу установления в 0 процессор начинает выполнение программы по этому адресу. Пространство с 0 по INI_ADDR-1 занимают подпрограммы обработки прерываний.

Процессор имеет регистровую память RRAM, которая состоит из шестнадцати 16-разрядных регистров. Регистры периферийных устройств занимают часть адресного пространства DRAM. Для быстрой загрузки адресов таких регистров они занимают старшие адреса пространства DRAM. Так, регистр разрешения прерываний INTENA имеет адрес INTENA_ADDR=X’FFFC’. Разрешение всех прерываний выполняется тремя командами:

ADDI 1,0,# -4; --адрес INTENA в регистр 1

ADDI 2,0 # -1; --запись FFFF в регистр 2

SD 2,1,#0 ; --разрешение прерываний

4. Структура процессора.

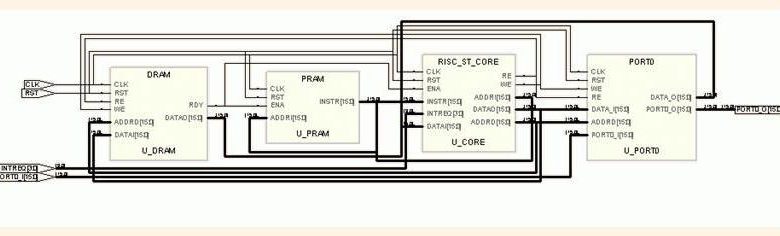

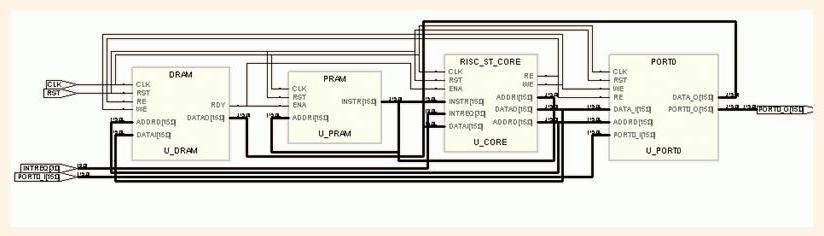

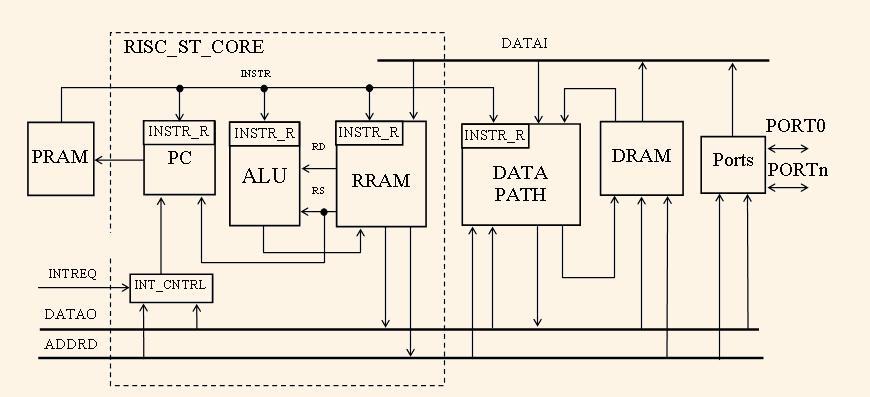

Процессор RISC_ST_CPU состоит из ядра RISC_ST_CORE, ОЗУ программ PRAM, ОЗУ данных DRAM и периферийных устройств (рис. 1). Состав периферийных устройств зависит от применения процессора, и в данном случае вмещает только порт ввода-вывода PORT0.

Ядро процессора составляют арифметико-логическое устройство ALU, блок регистровой памяти RRAM, блок счетчика команд РС и блок управления прерыванями INT_CNTRL (рис. 2).

В традиционных микропроцессорах все управление, включая регистр и дешифратор команд, сосредоточено в одном устройстве управления. Как правило, это устройство реализовано как микропрограммный автомат, благодаря простоте его разработки и модификации. Но при его реализации в СНК, как аппаратные затраты, так и критическая задержка схем могут оказаться довольно большими, что объясняется следующими особенностями СНК и RІSC-процессоров.

Задержку в линиях связи в ПЛИС можно оценить как пропорциональную их длине и она может быть большей, чем суммарная задержка в логических схемах. Когда управление сосредоточить в одном блоке управления, то его многочисленные входы и выходы необходимо подключать к остальным блокам микропроцессора через длинные маршруты с большими задержками. Кроме того, разветвленные маршруты не подвергаются эффективному трассированию, а когда количество нагрузок на один выход блока большое, то это также увеличивает общую задержку.

Так как в процессоре RISC_ST время выполнения команды не превышает одного такта, а аппаратные очистка и восстановление состояния конвейера команд при изменении контекста не предполагаются, то основную схему устройства управления можно свести к комбинационной схеме, которая дешифрирует код команды.

При этом для минимизации задержки в критических путях предлагается структура процессора с распределенным управлением. В каждом из блоков PC, ALU и RRAM находится отдельный регистр команд INSTR_R и локальное устройство управления. Также, благодаря простоте формата команд, их дешифрация и управление их выполнением несложные, а задержка в схемах управления не преобладает в общей задержке критического пути.

Регистры процессора формируют границы ступеней его конвейера. В первый уровень регистров входят регистр адреса-счетчик команд РС, второй уровень формирует регистр адреса команды, который входит в схему PRAM, а третий уровень сформирован регистрами команды ІNSTR_R. Четвертый уровень — это регистры блока RRAM, которые принимают результаты обработки данных в АЛУ, а также регистры данного и адреса, которые входят в состав DRAM, и в которые записываются данные и адрес при выполнении команд SD и LD.

5. Временная диаграмма выполнения команд.

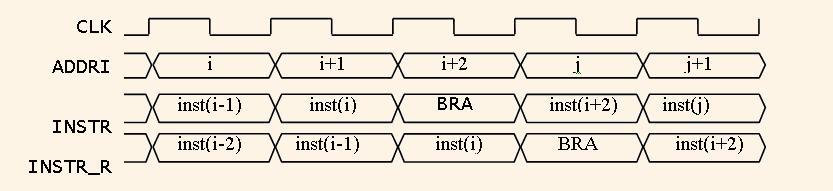

В процессоре реализуется двухуровневый конвейер команд. При выполнении потока команд в первом такте выполнения і-той команды по адресу ADDRI = і из PRAM выбирается команда іnst(і) и по шине INSTR записывается в регистры INSTR_R.

Во втором такте команда дешифруется и выполняется. В этом же такте, когда команда — не команда перехода, в РС вычисляется адрес, инкрементированный на 1, который равен адресу і+2-й команды. Когда выполняемая команда — команда перехода, например, BRA, то определяется адрес і+2 при нулевом условии перехода или j — при единичном условии перехода (рис. 3).

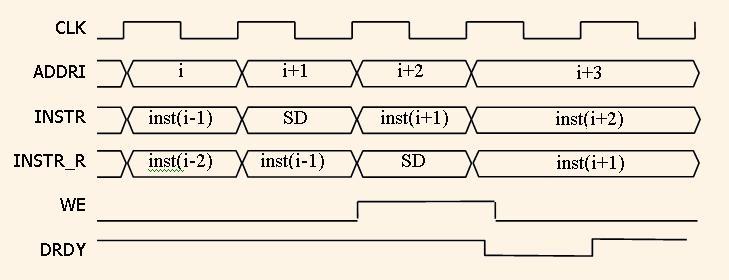

При выполнении команды SD записи в DRAM данное и адрес пересылаются с RRAM в DRAM в такте выполнения команды, а при чтении с DRAM адрес данного пересылается в том же такте, но считанное данное пересылается с DRAM в RRAM в следующем такте. При этом компилятор не должен вставлять команду, которая записывает результат ALU, такую как ADDI, SUB, AND и др., сразу после команды LD чтения DRAM.

Блок DRAM или его части, а также периферийные устройства могут иметь низкое быстродействие. Тогда они в ответ на сигнал записи WE или чтения RE должны выдавать сигнал готовности операции DRDY, нулевое состояние которого останавливает функционирование ядра RISC_ST_CORE. На рис. 4 показан пример временных диаграмм процессора при обращении к DRAM, который имеет латентную задержку 2 такта.

6. Описание структуры процессора RІSC_ST

Проект процессора предназначен для учебных или исследовательских целей, т.е. его практическое использование не предусматривалось. Тем не менее, по своим характеристикам процессор может быть сопоставим со многими коммерческими микропроцессорными ядрами. Так, его аппаратные затраты в ПЛИС Xіlіnx Vіrtex составляют около 190 ЭКЛБ плюс несколько блоков BLOCK_RAM, которые сохраняют программу и данные, а максимальное быстродействие — до 100 млн. команд в секунду. Он может отрабатывать до 30 млн. прерываний за секунду.

Модель микропроцессора RISC_ST представлена в двенадцати VHDL-файлах и содержит пакет проекта, модель ядра RISC_ST_CORE, пример микропроцессора RІSC_ST_CPU, поведенческие и синтезируемые модели блоков PRAM и DRAM, стенд для испытаний. Его структура показана на рис. 5.

Блок АЛУ ALU представляет собой комбинационную схему, которая выполняет разные функции с операндами RS и RD, которые поступают из блока регистровой памяти. Номер функции АЛУ, поступает из регистра команды INSTR_R, которая находится в блоке АЛУ. АЛУ выдает вектор условия CNVZ, который свидетельствует о признаках результата АЛУ.

Блок счетчика команд РС реализует управление потоком команд процессора. В состав этого блока входит также аппаратно реализованный стэк объемом шестнадцать двадцатиразрядных слов.

В традиционных RISC-процессорах в момент прерывания конвейер команд останавливается и состояние всех его ступеней сохраняется в программном стэке, чтобы после подпрограммы прерывания полностью восстановить состояние конвейера. Поэтому система прерываний в таких процессорах оказывается довольно сложной и медленной. В данном процессоре, чтобы обойти сложности, связанные с хранением и восстановлением конвейера команд, вводится разрешение прерываний таких команд, восстановление состояния которых не затруднительно. Разрешение не дается таким командам, которые являются командами перехода и следующим за ними командам, которые выполняются в такте задержки перехода. Для запрета прерываний устанавливается флаг F запрета прерываний в командах, которые стоят непосредственно перед указанными командами, т.е. считая конвейерную задержку на 1 такт. Этот флаг также устанавливается во всех командах подпрограмм обработки прерываний, так как все прерывания имеют единственный уровень приоритета и не могут быть прерванными.

Вектор прерываний равен адресу первой команды подпрограммы обработки прерываний. Этот адрес кратен восьми, т.е. на подпрограмму прерывания отведены восемь команд. Более длинная подпрограмма реализуется с помощью команд передачи управления в другую область памяти, т.е. CALL или LJMP.

Мультиплексор условия перехода определяет условие перехода в зависимости от поля cond команды и состояния вектора условий CNVZ, вычисленного в АЛУ по предыдущей команде. При выполнении команды CALL и вызове подпрограммы прерываний аппаратный стэк запоминает вектор состояния процессора, а при выполнении команд RET и RETI — выдает вектор состояния, который находится в вершине стэека. Вектор состояния процессора состоит из адреса возврата, который равен адресу команды, выполненной перед переходом, увеличенному на 1, и вектора условия CNVZ.

В традиционных RISC- процессорах при вызовах подпрограмм адрес возврата запоминается в одном из общих регистров и потом переписывается в программный стэк, т.е. для хранения и восстановления адреса возврата необходим большой промежуток времени. Благодаря аппаратно реализованному стэку, отработка прерываний в процессоре RISC_ST выполняется с высоким быстродействием, которое особенно важно при применении процессора в системах реального времени.

Блок управления прерываниями INT_CNTRL предназначен для фиксации сигналов прерываний, вычисления кода вектора прерываний и сигнала запроса прерывания и установки в 0 сигналов прерываний после выполнения соответствующих подпрограмм прерываний. Количество сигналов прерываний задается константой и может достигать нескольких десятков.

В состав ПЛИС серии Vіrtex входят быстродействующие синхронные ОЗУ BlockRAM, в которые записывается заданное начальний состояние во время конфигурирования. В одном блоке BlockRAM серии Vіrtex помещается до 256 команд, а блоке BlockRAM серии Vіrtex2 — до 2048 команд. Для хранения больших программ необходимо соединять параллельно несколько блоков BlockRAM.

7. Технические характеристики микропроцессора.

Основные технические характеристики микропроцессора при его реализации в ПЛИС фирмы Xіlіnx представлены в таблице 5, а в ПЛИС других фирм — в таблице 6.

Таблица 5. Основные технические характеристики микропроцессора при его реализации в ПЛИС фирмы Xilinx.

| Серия ПЛИС Xilinx | Аппаратные затраты, ЭКЛБ | Максимальная тактовая частота, МГц |

| Virtex | 190 | 60 |

| VirtexE | 190 | 77 |

| Virtex2 | 194 | 102 |

| Spartan3 | 194 | 45 |

Таблица 6. Основные технические характеристики в ПЛИС других фирм.

| Фирма и серия ПЛИС | Аппаратные затраты логических ячеек | Максимальная тактовая частота, МГц |

| Actel ACT3 | 1874 | 18 |

| Altera Apex 20KE | 548 | 52 |

| Altera Stratix GX | 717 | 98 |

| Lattice ORCA4 | 304 | 16 |

Анализ этих таблиц показывает, что при реализации микропроцессора в ПЛИС фирмы Xilinх достигается максимальная тактовая частота и минимальные аппаратные затраты. При этом принималось к вниманию, что по сложности приблизительно 23 логических ячейки фирмы Altera эквивалентны 10 ЭКЛБ. Нужно отметить, что проект микропроцессора конфигурируется без изменений (кроме модулей памяти) в ПЛИС любой серии.

8. Возможности изменения архитектуры микропроцессора.

Благодаря настройке архитектуры микропроцессора под задачу пользователя можно уменьшить аппаратные затраты и повысить быстродействие микропроцессора. Поэтому проект данного микропроцессора нужно выполнить с возможностью настройки в широких пределах.

Так, система команд и структура АЛУ позволяют добавить в перечень команд новые команды. Это такие команды, как логические функции, команды арифметического и циклического сдвига на один или несколько разрядов, команда поиска старшей значащей единицы, умножение, деление, команды загрузки констант, байтов с распространением знака, и т.п.. При изменении блока РС можно программировать глубину стэка, добавить к системе команд другие условия перехода, прибавить команду чтения констант из области памяти программ, вставить счетчик итераций для аппаратной поддержки программных циклов и увеличить объем стэка для хранения состояния этого счетчика при вызовах подпрограмм.

При изменении блока регистровой памяти можно выполнить эту память из двух страниц и переключать страницы при отрабатывании прерываний, благодаря чему можно увеличить быстродействие за счет автоматического сохранения состояния регистровой памяти; прибавить схему замедления активности процессора с целью энергосбережения; прибавить счетчик для слежения за активностью микропроцессора для повышения его надежности.

Нужно отметить, что блоки BlockRAM имеют 2 независимые порта доступа. Один из этих портов может быть использован для начальной загрузки PRAM с внешнего ОЗУ. Также в таком PRAM может быть организована оверлейна структура программы, для чего дополнительный блок прямого доступа к памяти должен подгружать фрагменты программы с внешнего ОЗУ на фоне выполнения программы. При более сложной организации управления можно PRAM реализовать в виде кэш-памяти, причем, в случае непопадания в кэш-память, процессор должен останавливаться, а автомат управления кеш-памятью должен переписывать отсутствующие строки с внешнего ОЗУ.

При более сложной модернизации к ядру микропроцессора прибавляются специализированные конфигурируемые вычислительные блоки для выполнения некоторых функций, которые нуждаются в высокой производительности для своего выполнения — аппаратных ускорителях. При этом управление таким блоком может быть как по специальной команде, так и путем записи управляющей информации в регистры, которые находятся в адресном пространстве периферийных устройств. Некоторые сложные команды могут выполняться в блоке ускорителя, тогда адреса данных поступают из ядра микропроцессора таким самым образом, как при выполнении команд записи данных в ОЗУ. Во время выполнения функции данные могут поступать параллельно с двух портов блока DRAM.

При выполнении сложного периодического алгоритма адресация блока DRAM может происходить с помощью специального генератора адресов блока ускорителя для организации конвейерной обработки. При этом для упрощения управления процессором его ядро тормозится.

Нужно отметить, что в ПЛИС, например, Virtex2, широко применяются аппаратные блоки умножения, причем один блок умножения приходится на 180-250 ЭКЛБ. Поэтому в микропроцессоре RISC_ST имеет смысл использовать команды умножения, которые реализуются на таких блоках. Эти блоки также эффективно использовать в блоке аппаратного ускорителя.

При изменении архитектуры микропроцессора его аппаратные затраты могут изменяться в пределах 190-500 ЭКЛБ. Тогда, если в его структуре будет использовано 1 или 2 блока умножения, аппаратные ресурсы ПЛИС будут использованы наиболее эффективно. С этой точки зрения вычислительные заготовки микропроцессоров другой архитектуры имеют недостаток — из-за того, что их аппаратные затраты превышают 500 ЭКЛБ и иногда достигают 3-4 тысячи ЭКЛБ, ресурсы блоков умножения ПЛИС используются нерационально.

Вычислительный модуль 16-разрядного RISC-микропроцессора. (zip — файл)