Однотактная синхронизация против двухтактной

| Назад | Cодержание |

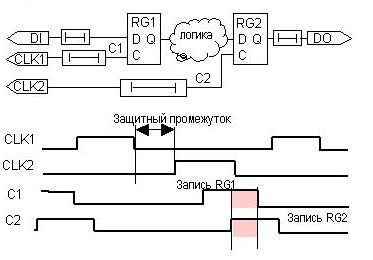

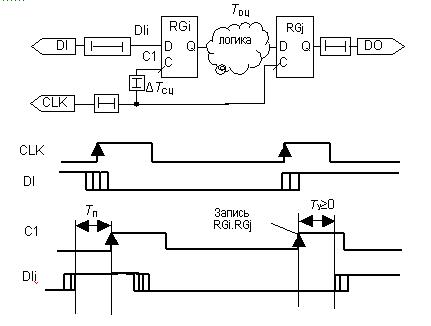

VHDL ДЛЯ СИНТЕЗАОднотактная синхронизация против двухтактнойВ сентябре 1979 г. в лаборатории спец-ЭВМ кафедры вычислительной техники КПИ под руководством Ю.С.Каневского приступили к системной отладке самого скоростного в стране опытного образца процессора БПФ, собранного из 2000 микросхем серии К155. Отладка шла, в целом, успешно. Но процессор упорно отказывался работать стабильно. Как ни меняли конструкцию системы синхронизации, как не варьировали период и скважность синхросерии — данные нет-нет, да проскакивали лишний уровень регистров. Второе решение — никогда больше в лаборатории Ю.С.Каневского не применять двухтактную синхронизацию… Проектирование микросхем и в частности, систем на кристалле (СНК) характеризуется тем, что ошибка в проекте обходится слишком дорого, а ее локализация в микросхеме и выяснение ее причин очень затруднительны. Поэтому основным правилом проектирования является то, что поведение ВУ в кристалле должно быть предсказуемым. В вычислительной технике используются, в основном, два принципа синхронизации вычислительных устройств (ВУ): двухтактной и однотактной синхронизации. Эти принципы обеспечивают различный уровень предсказуемости поведения ВУ и их необходимо рассмотреть подробнее. В вычислительном устройстве можно выделить группы регистров и триггеров, которые образуют уровни. Причем, при их соответствующем тактировании информация передается от одного уровня к другому, претерпевая по пути обработку в логических схемах. При двухтактной синхронизации соседние уровни регистров и триггеров синхронизируются различными синхросигналами (рис. 1).  Благодаря двухтактной синхронизации, триггеры могут быть выполнены по простейшей электрической схеме, т.е. как асинхронные, принимающие данные по уровню синхросерии. Задержки в линиях соединений могут превосходить задержки в логических схемах и триггерах. Эти задержки трудно выполнить нормированными в заданных пределах, а при реализации в ПЛИС — это почти невозможно. Поэтому принцип двухтактной синхронизации применяется только тогда, когда защитный промежуток между фазами достаточно велик. А это приводит к существенному уменьшению быстродействия ВУ по сравнению с максимально возможным. Если в ВУ применяются RS — триггеры и другие асинхронные триггеры, например, защелки, то такое ВУ необходимо отнести к схеме с двухтактной синхронизацией. Даже если в такой схеме используется один синхросигнал, то второй синхросигнал присутствует неявно. Например, его могут получать инвертированием первого синхросигнала. При разработке проектов для ПЛИС двухтактная синхронизация практически никогда не применяется, так как трудно получить проект с гарантированной работоспособностью. В некоторых ВУ используется асинхронный способ вычислений на логическом уровне, благодаря чему понижается энергопотребление до минимума. Но разработка таких ВУ не поддерживается стандартными САПР и тем более — САПР для ПЛИС.  При однотактной синхронизации все триггеры ВУ выполнены как синхронные и тактируются фронтом одного синхросигнала (рис. 2). При этом условием правильности функционирования ВУ является неравенство критической задержки: max( TT і + TD і , j + TП j ± Δ TC і , j ) < TC, (1) где TT і — задержка от фронта синхросигнала до выхода i-го триггера, TD і , j — задержка сигнала в логических схемах и линиях связи между i -м и j — м триггером, TП j — время предустановки сигнала на входе j-го триггера относительно фронта синхросигнала, Δ TC і , j — относительная задержка между синхросигналами, приходящими на эти триггеры, называемая перекосом фазы (clock skew), TC — заданный период синхросигнала, при условии, что время удержания сигнала на входе триггера ТУ удовлетворяет заданным ограничениям. В современных микросхемах сеть передачи синхросигнала от источника до всех триггеров выполняется с особой тщательностью и она обеспечивает минимальный перекос фаз, находящийся в пределах допустимого. Благодаря этому, формула (1) упрощается до следующей формулы: max( TT і + TD і , j + TП j ) < TC (2) Временной анализ проектов микросхемПредсказание правильности поведения ВУ с однотактной синхронизацией во всех САПР микросхем основано, прежде всего, на временном анализе задержек схемы ВУ, который выполняет программа временного анализа. Эта программа по известным задержкам между всеми элементами проекта ВУ, включая задержки в проводниках, выполняет проверку условия (2). Также вычисляются задержки от входных выводов микросхемы до входов триггеров и от выходов триггеров до выходных выводов микросхем. Задержки определяются как маршруты между вершинами графа схемы ВУ, дуги которого нагружены соответствующими задержками вентилей или проводников. Во многих ВУ используются сложные логические схемы, которые можно представить многовершинными двудольными графами с большим числом ребер. В этом случае количество маршрутов, по которым определяются задержки, представленных ребрами в двудольном графе, может достигать многих миллионов. Из-за перебора всех маршрутов временной анализ ВУ может длиться довольно долго. Если в ВУ существует перекос фаз, то временной анализ усложняется, так как он выполняется по более сложной формуле (1). Во многих САПР автоматический учет перекоса фаз не выполняется или проводится только для отдельно выбранных маршрутов. Если ВУ состоит из нескольких связанных между собой модулей, в пределах которых действуют разные синхросерии, то дополнительно проверяется условие (1), в котором Δ TC і , j — относительная задержка между фронтами двух синхросерий, а задержки определяются по маршрутам сигналов между парами блоков. Часто, операнд записывается в триггер i и хранится в нем несколько тактов, в течение которых сигнал операнда распространяется через логическую схему до триггера j, в который операнд записывается также через несколько тактов. Очевидно, что такой маршрут желательно удалить из временного анализа или анализировать отдельно, так как через него практически никогда не проходит критическая задержка. Такие маршруты выделяют в виде множества многотактовых маршрутов (multіcycle paths), называемых также ложными маршрутами (false paths). В результате временного анализа подтверждается, что схема ВУ работает с однотактной синхронизацией, что в ней отсутствуют критические перекосы фаз, а также фиксируются критический путь и его задержка, которые характеризуют быстродействие ВУ. fmax = 1 / TC mіn. Стадия размещения вентилей логической схемы по площади кристалла и трассировки межсоединений является ответственным этапом проектирования микросхемы и прошивки ПЛИС, так как от нее зависят все основные характеристики СНК. В то же время, это одна из самых трудоемких стадий. Она сводится к серии последовательных приближений к эффективному варианту размещения в плоскости микросхемы графа соединения вентилей . Одним из критериев оптимизации размещения и трассировки является минимум задержки критического пути. На основе временного анализа выполняется автоматическая оптимизация быстродействия схемы ВУ путем сокращения длины найденных критических путей. Поэтому для ускорения и улучшения оптимизации желательно минимизировать количество проверяемых маршрутов, например, отмечая многоцикловые маршруты и выделяя критические маршруты, требующие оптимизации. Конвейеризация вычислений, которая сводится к «расщеплению» сложных логических схем промежуточными конвейерными регистрами, существенно (от десятков до тысяч раз) сокращает число проверяемых маршрутов. Поэтому в конвейерных ВУ достигается прирост производительности не только благодаря укорачиванию маршрутов, но и за счет улучшения работы программы, оптимизирующей проект ВУ. Исходя из вышеизложенных особенностей проектирования микросхем, разработчики фирм — производителей микросхем предлагают следующие рекомендации :

Анатолий Сергиенко |

| Назад | Cодержание |