Реализация выражения в аппаратной модели VHDL

| Назад | Cодержание | Следующая |

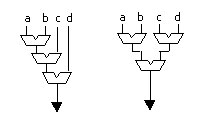

Изучение VHDLРеализация выражения в аппаратной модели VHDLЕсли выражение не упрощается при компиляции до константы или другого объекта, то оно реализуется в аппаратной модели в виде логических комбинационных схем. Операции в выражениях отображаются в схемы, выполняющие эти операции над операндами соответствующих типов. Логические операции реализуются в соответствующих элементах: and — в элементе «И», not — элементе «НЕ» и т.д. При операциях над битовыми или булевскими данными реализуются одиночные логические элементы. При выполнении операции над операндами регулярного типа каждому элементу операнда ставится в соответствие один логический элемент. Операции равенства и неравенства реализуются с помощью соответствующего числа элементов «И» с объединением их выходов в элементе «ИЛИ». Операции «больше» или «больше или равно» выполняются с помощью многоразрядной схемы сумматора-вычитателя, выход переполнения которой соответствует булевскому результату этой операции. Операции, сложения, вычитания, изменения знака выполняются с помощью схемы сумматора, а операция умножения — с помощью комбинационного умножителя. При этом если операнды типа positive, то умножение выполняется на умножителе без учета знака, а если типа integer — на умножителе со знаком. Операция абсолютного значения abs выполняется на схеме получения положительного числа из отрицательного и мультиплексора, который в зависимости от знака числа пропускает результат на выход схемы. Операция деления, модуля, остатка и возведения в степень, которые соответствуют сдвигу объекта, представленного двоичным числом, реализуются в схеме сдвигателя. При этом, если операнд типа integer, то сдвиг вправо реализуется с учетом знака. Операция конкатенации пары операндов регулярного типа соответствует объединению двух шин, пересылающих эти операнды, в одну, состоящую из исходных шин. При выполнении операций сложения и вычитания разрядность результата должна быть равна максимальной разрядности операндов. Операнды операции умножения должны иметь суммарную разрядность, равную разрядности произведения. Если операнды объявлены как тип integer без диапазона, то им соответствуют 32-разрядные типы и соответствующие 32-разрядные схемы реализации операций. Для минимизации оборудования рекомендуется принять объявление переменной с диапазоном: например, если переменные объявлены как : variable a, b: integer range (-128 to 127); то выражение a + b выполняется на 8-разрядном сумматоре. Сложное выражение от нескольких операндов при отсутствии скобок и с равноприоритетными операциями выполняется последовательно слева направо. Ему соответствует схема из цепочки модулей, выполняющих эти операции. Вставка скобок в это выражение задает приоритет выполнения операций, который отображается в аппаратную схему. Благодаря этому результирующая схема имеет вид дерева из модулей, задержка логических схем которого может быть намного меньше, чем в исходной схеме. a + b + c + d і ( a + b ) + ( c + d ).  Вставка скобок в выражение является одним из способов управления ходом синтеза, выполняемого компилятором-синтезатором.

Анатолий Сергиенко |

| Назад | Cодержание | Следующая |