Однотактна синхронізація проти двотактної

| Назад | Зміст |

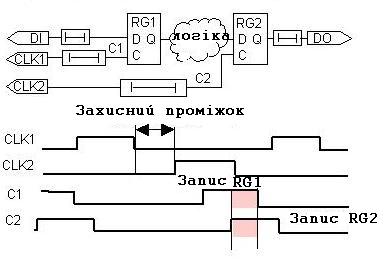

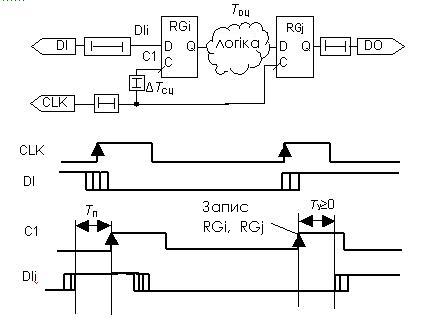

Вивчення VHDLОднотактна синхронізація проти двотактноїУ вересні 1979 р. у лабораторії спец-ЕОМ кафедри обчислювальної техніки КПІ під керівництвом Ю.С.Канєвського приступили до системного налагодження найшвидкісного в країні дослідного зразка процесора ШПФ, зібраного з 2000 мікросхем серії К155. Налагодження йшло, в цілому, успішно. Але процесор вперто відмовлявся працювати стабільно. Як не міняли конструкцію системи синхронізації, як не варіювали період і скважність синхросерії, – дані раз по раз, та проскакували зайвий рівень регістрів. Друге рішення – ніколи більше в лабораторії Ю.С.Канєвського не застосовувати двотактну синхронізацію… Проектування мікросхем і, зокрема , систем на кристалі (СНК) характеризується тим, що помилка в проекті обходиться занадто дорого, а її локалізація в мікросхемі і з’ясування її причин дуже утруднені. Тому основним правилом проектування є те, що поводження ОП в кристалі повинне бути передбачуваним. В обчислювальній техніці використовуються, в основному, два принципи синхронізації обчислювальних пристроїв (ОП): двотактної і однотактної синхронізації. Ці принципи забезпечують різний рівень передбачуваності поводження ОП і їх необхідно розглянути детальніше. В обчислювальному пристрої можна виділити групи регістрів і тригерів, які утворюють рівні. Причому, при їх відповідному тактуванні інформація передається від одного рівня до іншого, зазнаючи змін на шляху обробки в логічних схемах. При двотактній синхронізації сусідні рівні регістрів і тригерів синхронізуються різними синхросигналами (рис. 1).  Завдяки двотактній синхронізації, тригери можуть бути виконані за найпростішою електричною схемою, тобто як асинхронні, приймаючі дані за рівнем синхросерії. Затримки в лініях з’єднань мікросхем можуть перевершувати затримки в логічних схемах і тригерах. Ці затримки важко виконати нормованими в заданих межах, а при реалізації в ПЛІС – це майже неможливо. Тому принцип двотактної синхронізації застосовується тільки тоді, коли захисний проміжок між фазами досить великий. А це приводить до істотного зменшення швидкодії ОП в порівнянні з максимально можливим. Якщо у ОП застосовуються RS – тригери і інші асинхронні тригери, наприклад, защіпка, то такий ОП необхідно віднести до схеми із двотактною синхронізацією. Навіть якщо в такій схемі використовується один синхросигнал, то другий синхросигнал є присутнім неявно. Наприклад, його можуть одержувати інвертуванням першого синхросигнала. При розробці проектів для ПЛІС двотактна синхронізація практично ніколи не застосовується, тому що важко одержати проект із гарантованою працездатністю. В деяких ОП використовується асинхронний спосіб обчислень на логічному рівні, завдяки чому знижується енергоспоживання до мінімуму. Але розробка таких ОП не підтримується стандартними САПР і тим більше – САПР для ПЛІС.  При однотактній синхронізації всі тригери ОП виконані як синхронні і тактуются фронтом одного синхросигнала (рис. 2). При цьому умовою правильності функціонування ОП є нерівність критичної затримки: max( TT і + TD і , j + TП j ± Δ TC і , j ) < TC, (1) де TT і – затримка від фронту синхросигнала до виходу і- го тригера, TD і , j – затримка сигналу в логічних схемах і лініях зв’язку між і -м та j – м тригером, TП j – час предустановки сигналу на вході j- го тригера відносно фронту синхросигнала, Δ TC і , j – відносна затримка між синхросигналами, що приходять на ці тригери, яка називається перекосом фази (clock skew), TC – заданий період синхросигнала, за умови, що час утримання сигналу на вході тригера ТУ задовольняє заданим обмеженням. В сучасних мікросхемах мережа передачі синхросигнала від джерела до всіх тригерів виконується з особливою старанністю і вона забезпечує мінімальний перекіс фаз, який перебуває в межах припустимого. Завдяки цьому, формула (1) спрощується до наступної формули: max( TT і + TD і , j + TП j ) < TC (2) Часовий аналіз проектів мікросхем.Передбачення правильності поведінки ОП з однотактною синхронізацією у всіх САПР мікросхем засновано, насамперед , на аналізі часових затримок схеми ОП, який виконує програма часового аналізу. Ця програма по відомим затримкам між всіма елементами проекту ОП, включаючи затримки в провідниках, виконує перевірку умови (2). Також обчислюються затримки від вхідних виводів мікросхеми до входів тригерів і від виходів тригерів до вихідних виводів мікросхем. Затримки визначаються як маршрути між вершинами графа схеми ОП, дуги якого навантажені відповідними затримками вентилів або провідників. У багатьох ОП використовуються складні логічні схеми, які можна представити багатовершинними дводольними графами з великою кількістю ребер. У цьому випадку кількість маршрутів, по яких визначаються затримки, представлених ребрами у дводольному графі, може досягати багатьох мільйонів. Через перебір всіх маршрутів часовий аналіз ОП може тривати досить довго. Якщо в ОП існує перекiс фаз, то часовий аналіз ускладнюється, тому що він виконується по більш складній формулі (1). В багатьох САПР автоматичний облік перекосу фаз не виконується або проводиться тільки для окремо обраних маршрутів. Якщо ОП складається з декількох зв’язаних між собою модулів, у межах яких діють різні синхросерії, то додатково перевіряється умова (1), у якій Δ TC і , j – відносна затримка між фронтами двох синхросерій, а затримки визначаються за маршрутами сигналів між парами блоків. Часто, операнд записується в тригер і й зберігається в ньому кілька тактів, протягом яких сигнал операнду поширюється через логічну схему до тригера j, у який операнд записується також через кілька тактів. Вочевидь, що такий маршрут бажано видалити з часового аналізу або аналізувати окремо, тому що через нього практично ніколи не проходить критична затримка. Такі маршрути виділяють у множину багатотактових маршрутів (multіcycle paths), які називаються також помилковими маршрутами (false paths).

В результаті часового аналізу підтверджується, що схема ОП працює з однотактною синхронізацією, що в ній відсутні критичні перекоси фаз, а також фіксуються критичний шлях і його затримка, які характеризують швидкодію ОП. fmax = 1 / TC mіn. Стадія розміщення вентилів логічної схеми по площі кристала і трасування міжз’єднань є відповідальним етапом проектування мікросхеми і конфігурування ПЛІС, тому що від неї залежать всі основні характеристики СНК. У той же час, це одна із найтрудомісткіших стадій. Вона зводиться до серії послідовних наближень до ефективного варіанта розміщення в площині мікросхеми графа з’єднання вентилів . Одним із критеріїв оптимізації розміщення і трасування є мінімум затримки критичного шляху. На основі часового аналізу виконується автоматична оптимізація швидкодії схеми ОП через скорочення довжини знайдених критичних шляхів. Тому для прискорення і поліпшення оптимізації бажано мінімізувати кількість маршрутів, що перевіряються, наприклад, відзначаючи багатоциклові маршрути і виділяючи критичні маршрути, що вимагають оптимізації. Конвеєризація обчислень, що зводиться до “розщеплення” складних логічних схем проміжними конвеєрними регістрами, істотно (від десятків до тисяч разів) скорочує число маршрутів, що перевіряються. Тому в конвеєрних ОП досягається приріст продуктивності не тільки завдяки скорочуванню маршрутів, але й за рахунок поліпшення роботи програми,яка оптимізує проект ОП. Виходячи з вищевикладених особливостей проектування мікросхем, розробники фірм – виробників мікросхем пропонують наступні рекомендації :

– Застосовувати тільки однотактну синхронізацію і бажано, тільки один синхросигнал.

Анатолій Сергієнко |

| Назад | Зміст |