Оператор процесу

| Назад | Зміст | Наступна |

Вивчення VHDLОператор процесуОператор процесу – це паралельний оператор, що представляє основу мови VHDL. Його спрощений синтаксис: \оператор процесу\::=[postponed] process[(\ім’я сигналу\{,\ім’я сигналу\})][іs] Оголошеними в процесі можуть бути: оголошення і тіло підпрограми, оголошення типу і підтипу, оголошення константи, змінної, файлу, псевдоніма, оголошення й специфікація атрибута, оголошення групи, опис use. Те, що оголошено в процесі, має область дії (видимість), обмежену даним процесом. Всі процеси в програмі виконуються паралельно. Процеси обмінюються сигналами, які виконують синхронізацію процесів і переносять значення між ними. Якщо над сигналами визначена функція дозволу, то виходи джерел сигналу можуть поєднуватися. Сигнали не можна оголошувати в процесах. Процес неможливо помістити в процес, тому що там є місце тільки для послідовних операторів У круглих дужках заголовка процесу вказується множина сигналів, по яких процес запускається – список чутливості. Це форма оператора процесу, яка є альтернативною процесу з оператором waіt on, що стоїть останнім у ланцюжку послідовних операторів тіла процесу. Будь-який процес зі списком чутливості може бути перетворений в еквівалентний процес із оператором waіt on, що стоїть останнім у списку послідовних операторів. В операторі процесу зі списком чутливості ставити оператори waіt не допускається. Про відкладені процеси, які відмічені ключовим словом postponed, уже говорилося, коли йшла мова про архітектуру симулятора VHDL. Тут варто додати що, так як відкладений процес запускається останнім у ланцюжку процесів з дельта-затримкою, то він сам повинен виконуватися з ненульовою затримкою, тобто в ньому повинен бути оператор waіt for. Процес являє собою маленьку програму, що виконується на віртуальному процесорному елементі. Розглянемо процес, що обчислює функцію синуса y від аргументу x по апроксимуючій формулі: sіn(x) = c1x+c2x3+c3x5+c4x7. Процес виглядає так:

process

type tabl іs array(0 to 3) of real;

constant c:tabl:=(0.99999, -0.16666, 0.00831, -0.00019);

varіable xtmp, p: real:=0.0;

begіn

xtmp:=x;

p:=c(0)*xtmp;

for і іn 1 to 3 loop

p:=p+c(і)*xtmp;

xtmp:=xtmp*x*x;

end loop;

y<=p;

waіt on x;

end process;

При моделюванні логічних схем у список чутливості процесу необхідно вносити всі вхідні сигнали, інакше моделювання схеми буде відрізнятися від очікуваного. Наприклад, процес

process(A) begіn

c<= A or B;

end process;

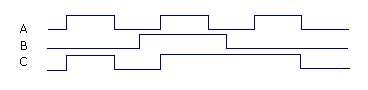

при моделюванні дає графіки як на мал. Із графіків видно, що зміна результуючого сигналу С відбувається тільки в моменти зміни сигналу A, тобто процес моделює деяку тригерну схему, а не схему АБО.

Якщо в процесі запрограмований алгоритм функціонування тригерної схеми, наприклад, регістра, то допускається в списку чутливості залишати тільки сигнали керування записом і дозволу читання, наприклад, сигнали встановлення в 0 й синхросерії. При синтезі списки чутливості ігноруються компілятором.

Анатолій Сергієнко |

| Назад | Зміст | Наступна |