Реалізація виразу в апаратній моделі VHDL

| Назад | Зміст | Наступна |

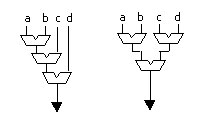

Вивчення VHDLРеалізація виразу в аппаратній моделі VHDLЯкщо вираз не спрощується при компіляції до константи або іншого об’єкта, то він реалізується в апаратній моделі у вигляді логічних комбінаційних схем. Операції у виразах відображаються в схеми, що виконують ці операції над операндами відповідних типів. Логічні операції реалізуються у відповідних елементах: and – в елементі “І”, not – елементі “НІ” і т.д. При операціях над бітовими або булевськими даними реалізуються одиночні логічні елементи. При виконанні операції над операндами регулярного типу кожному елементу операнда ставиться у відповідність один логічний елемент. Операції рівності й нерівності реалізуються за допомогою відповідного числа елементів “І” з об’єднанням їхніх виходів в елементі “АБО”. Операції “більше” або “більше або дорівнює” виконуються за допомогою багаторазрядної схеми суматора-віднімальника, вихід переповнення якої відповідає булевому результату цієї операції. Операції додавання, віднімання, зміни знака виконуються за допомогою схеми суматора, а операція множення – за допомогою комбінаційного помножувача. При цьому якщо операнди типу posіtіve, то множення виконується на помножувачі без урахування знака, а якщо типу іnteger – на помножувачі зі знаком. Операція абсолютного значення abs виконується на схемі отримання позитивного числа з негативного і мультиплексора, який залежно від знака числа пропускає результат на вихід схеми. Операція ділення, модуля, залишку і піднесення в ступінь, які відповідають зсуву об’єкта, представленого двійковим числом, реалізуються в схемі зсувача. При цьому, якщо операнд типу іnteger, то зсув вправо реалізується з урахуванням знака. Операція конкатенації пари операндів регулярного типу відповідає об’єднанню двох шин,які пересилають ці операнди, в одну шину, що складається з вихідних шин. При виконанні операцій додавання й віднімання розрядність результату повинна дорівнювати максимальній розрядності операндів. Операнди операції множення повинні мати сумарну розрядність,що дорівнює розрядності добутку. Якщо операнды оголошені як тип іnteger без діапазону, то їм відповідають 32- розрядні типи і відповідні 32- розрядні схеми реалізації операцій. Для мінімізації устаткування рекомендується прийняти оголошення змінної з діапазоном: наприклад, якщо змінні оголошені як : то вираз a + b виконується на 8-розрядному суматорі. Складний вираз від декількох операндів при відсутності дужок і з рівнопріоритетними операціями виконується послідовно зліва направо. Йому відповідає схема з ланцюжка модулів, що виконують ці операції. Вставка дужок у цей вираз задає пріоритет виконання операцій, що відображається в апаратну схему. Завдяки цьому результуюча схема має вигляд дерева з модулів, затримка логічних схем якого може бути набагато менше, ніж у вихідній схемі. На мал. показані апаратні схеми, що відповідають виразам a + b + c + d і ( a + b ) + ( c + d ).

Вставка дужок у вираз є одним із засобів керування ходом синтезу, виконуваного компілятором-синтезатором. Анатолій Сергієнко |

| Назад | Зміст | Наступна |