Що таке VHDL ?

| Назад | Зміст | Наступна |

Вивчення VHDLЩо таке VHDL ?Коротко про VHDLТрадиційно одним з етапів проектування засобів обчислювальної техніки є розробка електричних схем. Ця відповідальна робота пов’язана з великими затратами праці, контролем правильності й відповідності задуманому проекту, необхідністю чіткого і ємного опису створених схем, труднощами з їхнім супроводом і модернізацією. САПР обчислювальної техніки, як правило, мають засоби введення і редагування схем. Однак два десятиліття тому при розробці ЗВІС відмовилися від схемного проектування. Мова Very high speed integrated circuits Hardware Description Language (VHDL) була розроблена в 1983 р. на замовлення Міністерства оборони США з метою формального опису логічних схем для всіх етапів розробки електронних систем, починаючи з модулів мікросхем і закінчуючи великими обчислювальними системами. Вона є стандартною мовою з 1987 р. Стандартом 1993 р. закріплено багато її вдосконалень [1]. Поряд з мовою Verilog вона є базовою мовою при розробці апаратури сучасних обчислювальних систем. У чому переваги VHDL над схемним проектуванням?Проектування великих обчислювальних пристроїв (ОП) – За допомогою VHDL простіше й швидше ввести й перевірити великий проект. Десятьма рядками VHDL можна описати як 1, так і 100000 тригерів. Мікросхему з інтеграцією більше 10000 вентилів розробити тільки за допомогою електричних схем дуже важко через громіздкість схем. Проект на VHDL – об’єднання структури ОП і алгоритму його функціонування. Для ОП, описаного на VHDL, необов’язково виконувати перевірку правильності його функціонування, наприклад, шляхом його макетування. Щоб визначити, чи правильно ОП виконує заданий алгоритм, достатньо його VHDL -програму запустити на виконання в симуляторі VHDL. Відповідні САПР перетворять VHDL-опис у комплект документації для виготовлення дієвого пристрою. Проект на VHDL – самодокументований, тобто він не вимагає додаткового технічного опису або опису у вигляді схем. Нечіткість і недбалість опису виключаються, тому що проект на VHDL нескладно перевірити. Висока надійність проекту. Синтаксичний аналіз, моделювання й компіляція в логічну схему швидко виявляють помилки проекту. Проект на VHDL – універсальний проект. Розроблений один раз обчислювальний блок може бути використаний у багатьох інших проектах. При цьому багато структурних і функціональних параметрів блоку можуть бути настроюваними (параметри розрядності, об’єму пам’яті, елементна база, склад блоку й структура міжз’єднань). Проект на VHDL – портативний проект. Розроблений для однієї елементної бази, проект ОП легко переноситься на іншу елементну базу, напр. НВІС із різною технологією. Проект на VHDL – проект, що довго живе. Електрична схема завжди розробляється під конкретні елементну базу й інтерфейс. Відповідно до того, що елементна база змінюється за період 2-5 років, за цей же період застарівають і електричні схеми, що її використовують. Проект ОП на VHDL може бути повторно використаний через кілька років. Гарне технічне рішення (напр., винахід), описане на VHDL, може бути корисним протягом десятиліть. VHDL – універсальний засіб опису ОП на рівнях:

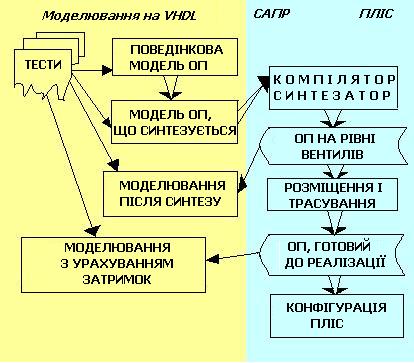

Хід проектування з використанням VHDL.На малюнку показана схема розробки проекту ОП, призначеного для виконання в програмованій логічній інтегральній схемі (ПЛІС).

Спочатку ОП описується у вигляді своєї поведінкової моделі, на якій відпрацьовується задуманий алгоритм функціонування ОП. Потім ця модель вручну переробляється в синтезовану модель ОП, описану на рівні регістрових передач. Така модель, будучи странсльованою компілятором-синтезатором, дає проектну документацію у вигляді файлу опису схеми ОП на рівні вентилів (EDIF – файл). При цьому автоматично виконується логічна оптимізація ОП. Одночасно цей файл автоматично перетвориться в VHDL- модель ОП на рівні вентилів. Проект ОП у вигляді Electronic Distribution International Format (EDIF) – файлу приймається як вхідний всіма САПР виготовлення ПЛІС і ЗВІС. Ці САПР виконують заміну вентилів на бібліотечні компоненти, їхнє розміщення на площі кристала, трасування міжз’єднань, проектування масок, перевірку відповідності проектним нормам і т.п. У результаті записуються файли проектної документації виготовлення кристала і його логічної моделі, що враховує затримки як у вентилях, так і в міжз’єднаннях. Ця модель також представляється на VHDL. Вартість помилок при проектуванні ЗВІС дуже висока, особливо на ранніх етапах. Тому всі етапи проектування – алгоритмічний, структурний, логічний, технологічний – супроводжуються моделюванням ОП за допомогою, так званого іспитового стенду (testbench). Цей стенд представляє VHDL-модель, складовими частинами якої є модель ОП, що тестується, і моделі генератора тестових сигналів і логічного аналізатора, що перевіряють правильність функціонування ОП. Причому на всіх етапах може використовуватися той самий іспитовий стенд і ті самі тестові файли. З яких причин VHDL використовується в сучасних САПР мікроелектроніки?Історично склалося, що в мікроелектронній індустрії найбільше поширення здобула мова Verilog. Півтора десятиліття тому ця мова виграла конкурентну боротьбу з іншими мовами завдання ОП, завдяки невеликим необхідним обчислювальним ресурсам колишніх робочих станцій і досить точним результатам моделювання ЗВІС. VHDL – більш універсальна й гнучка мова, але вона програвала у швидкодії мові Verilog, особливо при моделюванні на рівні вентилів і транзисторів. VHDL отримала широке поширення в університетах і дослідницьких установах, тому що це строга, струнка, універсальна й розширювана мова. Так, наприклад, з’явилися пакети VHDL для аналогового моделювання, моделювання багатозначної логіки. Крім того, симулятори VHDL були набагато дешевше симуляторів Verilog. Всі сучасні САПР мікроелектроніки мають компілятори як з Verilog, так і з VHDL. Програміст, що освоїв VHDL, без особливих зусиль може перейти до програмування мовою Verilog. На відміну від зворотнього. Найважливішими якостями VHDL у САПР виступають наступні:Гнучкість. Проект, описаний на VHDL, може бути легко настроєний під конкретні завдання споживача. Універсальна мова. VHDL – загальноприйнята мова для всіх основних фірм – виготовлювачів мікросхем ПЛІС, ПЛМ, замовлених ЗВІС як стандартна мова для завдання складних проектів. Проектування з VHDL – стійка тенденція в інженерній технології. Існують компілятори, що транслюють VHDL- програми в еквівалентні їм Verilog – програми. Моделювання з урахуванням затримок. Фірми – виготовлювачі мікросхем у своїх САПР забезпечують генерацію моделей результатів розміщення і трасування, описаних на VHDL. Стандартне підключення блоків. Конструкції мови, такі як entity, port map, configuration, забезпечують надійне й швидке стикування блоків, які розроблені різними фірмами й розробниками, у різному сполученні. Стандартне тестування. На всіх етапах розробки виконується тестування за однією методикою тими самими тестами. VHDL – стандарт майбутнього. Всі нові САПР засновані на технології трансляції опису ОП мовою опису апаратури. Використання VHDL – гарантія того, що через 5 і 10 років знайдеться САПР, що підтримує старі розробки.

Анатолій Сергієнко |

| Назад | Зміст | Наступна |