Обчислювальний модуль 16-розрядного RISC- мікропроцесора.

А. М. СЕРГІЄНКО

1. Призначення і назва RISC-мікропроцесора.

Учбовий RISC–мікропроцесор RISC_ST (student – скорочено – ST) призначений для вивчення основ побудови і проектування RISC–мікропроцесорів за допомогою VHDL. Він також призначений для експериментів з метою розробки і перевірки нових методів проектування ОС на СНК. За своїми технічними характеристиками і, насамперед, за архітектурою він відповідає процесорам для реалізації в СНК систем реального часу. Проект процесора орієнтований на реалізацію в ПЛІС фірми Xilinx, але може бути реалізований в ПЛІС інших фірм, а також замовлених НВІС.

Під архітектурою процесора розуміють набір основних відомостей, які необхідні для розробки цього процесора і його використання. Як правило, ці відомості вміщують в себе

- структуру процесора,

- інформацію про систему команд, систему переривань, адресний простір і порядок доступу до пам’яті,

- склад та схему підключення периферійного обладнання,

- організацію віртуальної адресації і кеш-пам’яті,

- латентні затримки виконання операцій і доступу до пам’яті,

- множину команд, які можуть виконуватися паралельно,

- механізми захисту доступу до ресурсів, зміни контекста, багатопотокової обробки та інше.

Архітектура RISC_ST характерна тим, що вона вміщує всі основні особливості RISC–процесорів, такі як простий формат команд, конвеєризація, виконання команд під час відпрацювання команди переходу, регістрова пам’ять. Для роботи в реальному часі процесор має підвищену швидкодію не тільки за рахунок однотактового виконання команд, але і завдяки апаратно реалізованому стеку та швидкодіючій системі переривань.

RISC_ST–процесор має 16-розрядні дані і команди. Такої розрядності досить для реалізації великої множини задач, що вирішуються в СНК.

Детально про розробку цього процесора описано в книзі: Сергиенко А.М. VHDL для проектирования вычислительных устройств. –Киев: ДиаСофт, -2003, -208 с.

Спроба його модифікації з розробкою асемблера детально викладена на форумі http://electronix.ru/forum/index.php?showtopic=60367&st=30

2. Система команд.

В процесорі множина команд розбита на чотири типи. Типи і поля команд вказані в таблиці 1, а перелік команд, їхнє кодування і короткий опис показані в таблиці 2. В полі F встановлюється прапор дозволу переривань, поле СОР означає код операції, в полях RD і RS показані адреси регістрів, поле Func кодує тип переходу або арифметичної операції, поля Imm і Disp задають 8-розрядні безпосередній операнд і зсув адреси, відповідно, а поле Cond – умову переходу.

Таблиця 1. Типи і поля команд

| Тип команди | Розряди команди | ||||

| 15 | 14-12 | 11-8 | 7-4 | 3-0 | |

| RR | F | COP | RD | RS | Func |

| RI | F | COP | RD | Imm | |

| BRA | F | COP | Cond | Disp | |

| JMP | F | COP | Cond | RS | Func |

Таблиця 2. Перелік команд, їхнє кодування і короткий опис

| Команда | Розряди команди | Опис | ||||

| Iм’я | Тип | 14-12 | 11-8 | 7-4 | 3-0 | |

| NOP | JMP | 000 | 0000 | 0000 | 0000 | Немає операції | CALL | JMP | 000 | Cond | RS | 0001 | Виклик підпрограми по {RS} |

| RET | JMP | 000 | Cond | – | 0010 | Повертання з підпрограми |

| RETI | JMP | 000 | Cond | – | 0100 | Повертання з підпрограми переривань |

| LJMP | JMP | 000 | Cond | RS | 1000 | Умовний перехід по {RS} |

| BRA | BRA | 001 | Cond | Disp | Умовний перехід за адресою {PC}+Disp | |

| LD | RR | 010 | RD | RS | Imm4 | Завантаження в регістр RD даного за адресою {RS}+Imm4 | SD | RR | 011 | RD | RS | Imm4 | Збереження даного з RD за адресою {RS}+Imm4 |

| LL | RI | 100 | RD | Imm | Завантаження Imm в молодший байт регістра RD | |

| LH | RI | 101 | RD | Imm | Завантаження Imm в старший байт регістра RD | ADDI | RR | 110 | RD | RS | Imm4 | Запис RS+Imm4 в RD | ALU | RR | 111 | RD | RS | Func | Запис RS (Func) RD в RD |

Регістрові команди RR виконують різні дії над вмістом регістрів RD і RS з записом результату в регістр RD (команди ALU і ADDI), а також пересилку даного між регістром RD і коміркою пам’яті даних з адресою з регістра RS (команди завантаження LD і збереження SD). Команда ALU виконує функцію логічного І – AND, виключного АБО – XOR, логічного і арифметичного зсуву вправо на один розряд – SRL, SRA, додавання і віднімання – ADD, SUB, додавання і віднімання з переносом – ADDC, SUBC.

В таблиці 3 представлено кодування функцій цієї команди. Команда ADDI додає до вмісту регістра RS чотирирозрядну безпосередню константу Imm4. При звертанні до пам’яті даних в командах LD і SD до адреси даного додається безпосередній приріст Imm4.

Таблиця 3. Кодування функцій команди ALU.

| Ім’я | Func | Опис |

| AND | 0000 | RD and RS -> RD |

| XOR | 0001 | RD xor RS -> RD |

| SRL | 0010 | ‘0’ & RS(15..1) -> RD |

| SRA | 0011 | RS(15) & RS(15..1) -> RD |

| ADD | 1000 | RD + RS -> RD |

| SUB | 1001 | RD – RS -> RD |

| ADDC | 1010 | RD + RS +C -> RD |

| SUBC | 1011 | RD – RS – C -> RD |

За командами JMP виконується виклик підпрограми – CALL, повернення з неї – RET, повернення з підпрограми переривань – RETI та умовний перехід за абсолютною адресою – LJMP. При цьому адреса переходу береться з регістра RS. Умови переходу такі самі, як і в команді BRA.

Всі безпосередні операнди команд, крім Imm, є цілими числами зі знаком в доповнюючому коді.

Регістрові команди з безпосереднім операндом RI виконують завантаження в старший байт RD або молодший байт RD безпосереднього 8-розрядного операнду (команди LH і LL, відповідно).

Команда BRA виконує перехід відносно стану регістра адреси зі зсувом Disp за умовою Cond. В таблиці 4. показані можливі умови переходу.

Таблиця 4. Mожливі умови переходу.

| Ім’я | Cond | Опис |

| JUMP | 0001 | Безумовний перехід |

| NOP | 0000 | Немає переходу |

| EQ | 0011 | Результат Y=0 |

| NEQ | 0010 | Результат Y≠0 |

| LT | 0101 | Результат Y<0 |

| GE | 0100 | Результат Y>0 |

| LE | 0111 | Результат Y<0 |

| GT | 0110 | Результат Y>0 |

| CY | 1001 | Перенос |

Система команд процесора дає достатньо можливостей для вирішення широкого кола задач. Багато команд, що не вказані в табл. 2-4, можна розглядати як особливий випадок кодування цих команд або програмувати їх ланцюжком команд. Наприклад, команда зсуву вліво SLL RD; – це команда ADD RD,RD; команда пересилки MOV RD,RS; – це команда ADDI RD,RS,#0; команда встановлення в нуль регістра – це XOR RD,RD. Завантаження будь-якої константи С = 256*СH+CL виконується двома командами: LH RD, CH; LL RD, CL.

Як правило, в нульовому регістрі RISC–процесора зберігається нуль. Тоді команда інверсії NEG RD; – обчислюється як SUB RD,0; а команда порозрядного інвертування NOT RD; обчислюється парою команд: ADDI 1, 0, #-1; XOR RD, 1;.

Більш складні операції, такі як множення, ділення, обчислюються за підпрограмами. Крім того, коли (в залежності від застосування процесора) складні обчислення потребують підвищеної швидкодії, ці обчислення можуть бути реалізовані в периферійних пристроях, що спеціально розроблені для цього.

Архітектура RISC_ST припускає додавання інших команд, функцій ALU, умов переходу для збільшення функціональності, швидкодії, а також з навчальною та експериментальною метою.

3. Простір адрес.

Мікропроцесори для встроювання в апаратуру повинні мати підвищену надійність функціонування. Згідно з одним із правил забезпечення надійності, не припускається зміна програми в процесі її виконання. Найпростіше це досягається, коли програма зберігається в ПЗП або ОЗП, до якого немає прямого програмного доступу. Крім того, коли команди і дані зберігаються в окремих блоках пам’яті, то до них можна реалізувати паралельний доступ. Таким чином, процесор RISC_ST повинен мати окремі блок ОЗП програм PRAM і блок ОЗП даних DRAM. Розрядність процесора забезпечує адресацію до 65К слів PRAM і до 65К слів DRAM. Можна збільшити розмір DRAM, додаючи сторінкову адресацію.

Основна програма розміщується в адресному просторі PRAM, починаючи з адреси INIT_ADDR. За сигналом встановлення в 0 процесор починає виконання програми з цієї адреси. Простір з 0 по INIT_ADDR-1 займають підпрограми обробки переривань.

Процесор має регістрову пам’ять RRAM, що складається з шістнадцяти 16-розрядних регістрів. Регістри периферійних пристроїв займають частину адресного простору DRAM. Для швидкого завантаження адрес таких регістрів вони займають старші адреси простору DRAM. Так, регістр дозволу переривань INTENA має адресу INTENA_ADDR=X’FFFC’. Дозвіл усіх переривань виконується трьома командами:

ADDI 1,0,# -4; --адреса INTENA в регістр 1

ADDI 2,0 # -1; --запис FFFF в регістр 2

SD 2,1,#0 ; --дозвіл переривань

4. Структура процесора.

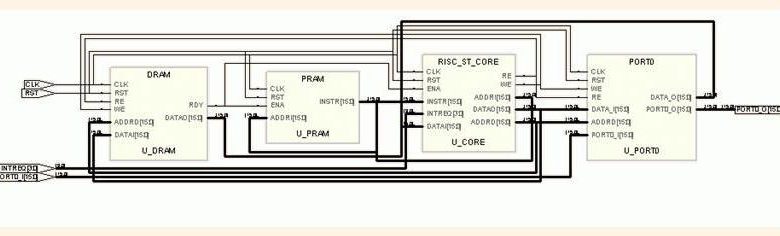

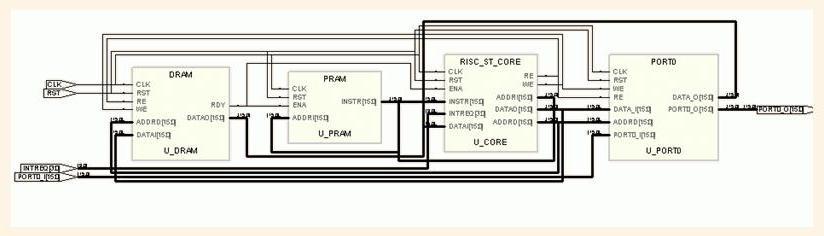

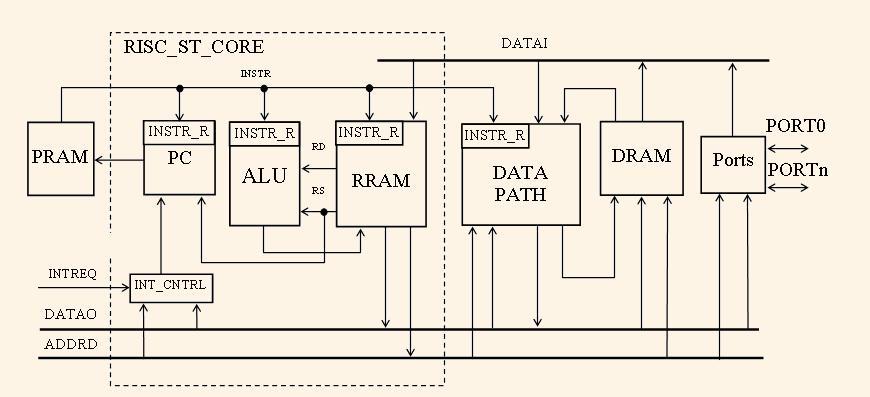

Процесор RISC_ST_CPU cкладається з ядра RISC_ST_CORE, ОЗП програм PRAM, ОЗП даних DRAM і периферійних пристроїв (рис. 1). Склад периферійних пристроїв залежить від застосування процесора і в даному випадку вміщує тільки порт вводу-виводу PORT0.

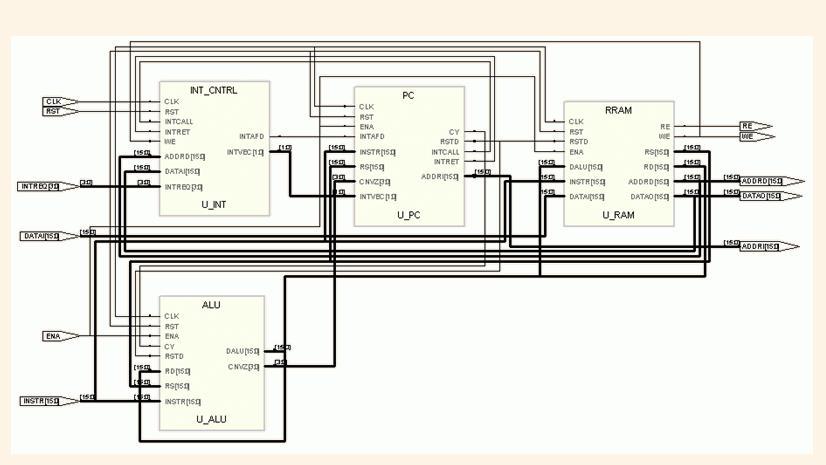

Ядро процесора складають арифметико-логічний пристрій ALU, блок регістровій пам’яті RRAM, блок лічильника команд РС і блок керування перериваннями INT_CNTRL (рис. 2).

В традиційних мікропроцесорах усе керування, включаючи регістр і дешифратор команд, зосереджене в одному пристрої керування. Як правило, цей пристрій реалізовано як мікропрограмний автомат, завдяки простоті його розробки і модифікації. Але при його реалізації в СНК, як апаратурні витрати, так і критична затримка схем можуть виявитись досить великими, що роз’яснюється наступними особливостями СНК і RISC-процесорів.

Затримку в лініях зв’язку в ПЛІС можна оцінити як пропорційну їхній довжині і вона може бути більшою, ніж сумарна затримка в логічних схемах. Коли керування зосередити в одному блоці керування, то його багаточисельні входи і виходи необхідно підключати до решти блоків мікропроцесора через довгі маршрути з великими затримками. Крім того, розгалужені маршрути не піддаються ефективному трасуванню, а коли кількість навантажень на один вихід блока велика, то це також збільшує загальну затримку.

Оскільки в процесорі RISC_ST час виконання команди не перевищує одного такту, а апаратні очистка і відтворення стану конвеєра команд при зміні контексту не передбачаються, то основну схему пристрою керування можна звести до комбінаційної схеми, що дешифрує код команди.

При цьому для мінімізації затримки в критичних шляхах пропонується структура процесора з розподіленим керуванням. В кожному з блоків PC, ALU і RRAM знаходиться окремий регістр команд INSTR_R і локальний пристрій керування. Також завдяки простоті формата команд, їхня дешифрація і керування їхнім виконанням нескладні, а затримка в схемах керування не превалює в загальній затримці критичного шляху.

Регістри процесора формують межі ступенів його конвеєра. В перший рівень регістрів входять регістр адреси – лічильник команд РС, другий рівень формують регістр адреси команди, що входить в схему PRAM, а третій рівень сформований регістрами команди INSTR_R. Четвертий рівень – це регістри блока RRAM, що приймають результати обробки даних в АЛП, а також регістри даного і адреси, що входять в склад DRAM, в які записуються дані і адреса при виконанні команд SD і LD.

5. Часова діаграма виконання команд.

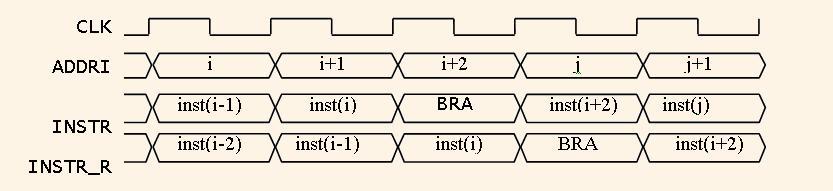

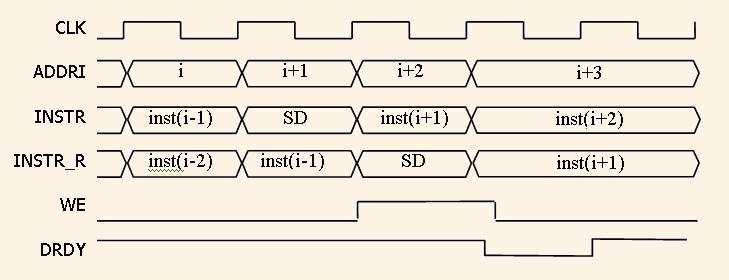

В процесорі реалізується дворівневий конвеєр команд. При виконанні потоку команд в першому такті виконання i-ї команди за адресою ADDRI = i з PRAM вибирається команда inst(i) і по шині INSTR записується в регістри INSTR_R. В другому такті команда дешифрується і виконується. В цьому ж такті, коли команда – не команда переходу, в РС обчислюється адреса, інкрементована на 1, що дорівнює адресі і+2-ї команди. Коли виконувана команда – команда переходу, наприклад, BRA, то визначається адреса i+2 при нульовій умові переходу або j – при одиничній умові переходу (рис. 3).

При виконанні команди SD запису в DRAM дане і адреса пересилаються з RRAM в DRAM в такті виконання команди, а при читанні з DRAM адреса даного пересилається в тому ж такті, але зчитане дане пересилається з DRAM в RRAM в наступному такті. При цьому компілятор не повинен вставляти команду, що записує результат ALU, таку як ADDI, SUB, AND та ін., одразу після команди LD читання DRAM.

Блок DRAM або його частини, а також периферійні пристрої можуть мати низьку швидкодію. Тоді вони у відповідь на сигнал запису WE або читання RE повинні видавати сигнал готовності операції DRDY, нульовий стан якого зупиняє функціонування ядра RISC_ST_CORE. На рис. 4 показаний приклад часових діаграм процесора при звертанні до DRAM, який має латентну затримку 2 такти.

6. Опис структури процесора RISC_ST

Проект процесора призначений для навчальних або дослідницьких цілей, тобто його практичне використання не передбачалось. Тим не менше, за своїми характеристиками процесор може бути порівняний з багатьма комерційними мікропроцесорними ядрами. Так, його апаратні витрати в ПЛІС Xilinx Virtex складають біля 190 ЕКЛБ плюс декілька блоків BLOCK_RAM, що зберігають програму і дані, а максимальна швидкодія – до 100 млн. команд на секунду. Він може відпрацьовувати до 30 млн. переривань за секунду.

Модель мікропроцесора RISC_ST представлена в дванадцяти VHDL–файлах і вміщує пакет проекта, модель ядра RISC_ST_CORE, приклад мікропроцесора RISC_ST_CPU, поведінкові і синтезуємі моделі блоків PRAM і DRAM, стенд для іспитів. Його структура показана на рис. 5.

Блок АЛП ALU є комбінаційною схемою, що виконує різні функції з операндами RS і RD, які надходять з блока регістрової пам’яті. Номер функції АЛП, надходить з регістра команди INSTR_R, що знаходиться в блоці АЛП. АЛП видає вектор умови CNVZ, що свідчить про ознаки результата АЛП.

Блок лічильника команд РС реалізує керування потоком команд процесора. У склад цього блоку входить також апаратно реалізований стек об’ємом шістнадцять двадцятирозрядних слів.

В традиційних RISC-процесорах у момент переривання конвеєр команд зупиняється і стан усіх його ступенів зберігається в програмному стеку, щоб після підпрограми переривання повністю відновити стан конвеєра. Тому система переривань у таких процесорах виявляється досить складною і повільною. В даному процесорі, щоб обійти складності, пов’язані зі зберіганням і відновленням конвеєра команд, вводиться дозвіл переривань таких команд, відновлення стану яких не створює труднощів. Дозвіл не дається таким командам, які є командами переходу і наступними за ними командами, що виконуються в такті затримки переходу. Для заборони переривань встановлюється прапор F заборони переривань у командах, що безпосередньо передують указаним командам, тобто враховуючи конвеєрну затримку на 1 такт. Цей прапор також встановлюється у всіх командах підпрограм обробки переривань, так як всі переривання мають однаковий рівень пріоритета і не можуть бути перерваними.

Вектор переривань дорівнює адресі першої команди підпрограми обробки переривань. Ця адреса кратна восьми, тобто на підпрограму переривань відведено вісім команд. Більш довга підпрограма реалізується за допомогою команд передачі керування в іншу область пам’яті, тобто CALL або LJMP.

Мультиплексор умови переходу визначає умову переходу в залежності від поля cond команди і стану вектора умови CNVZ, обчисленого в АЛП за попередньою командою. При виконанні команди CALL і виклику підпрограми переривань апаратний стек запам’ятовує вектор стану процесора, а при виконанні команд RET і RETI – видає вектор стану, що знаходиться в вершині стеку. Вектор стану процесора складається з адреси повернення, що дорівнює адресі команди, яка виконується, збільшеній на 1, і вектора умови CNVZ.

В традиційних RISC-процесорах при викликах підпрограм адреса повернення запам’ятовується в одному з загальних регістрів і потім переписується в програмний стек, тобто для зберігання і відновлення адреси повернення необхідний великий проміжок часу. Завдяки апаратно реалізованому стеку, відпрацювання переривань в процесорі RISC_ST виконується з високою швидкодією, що особливо важливо при застосуванні процесора в системах реального часу.

Блок керування перериваннями INT_CNTRL призначений для фіксації сигналів переривань, обчислення кода вектора переривань і сигналу запиту переривання та встановлення в 0 сигналів переривань після виконання відповідних підпрограм переривань. Кількість сигналів переривань задається константою і може досягати кількох десятків.

В склад ПЛІС серії Virtex входять швидкодіючі синхронні ОЗП BlockRAM, в які записується заданий початковий стан під час конфігурування. В одному блоці BlockRAM серії Virtex вміщується до 256 команд, а в блоці BlockRAM серії Virtex2 – до 2048 команд. Для зберігання великих програм необхідно з’єднувати паралельно декілька блоків BlockRAM.

7. Технічні характеристики мікропроцесора.

Основні технічні характеристики мікропроцесора при його реалізації в ПЛІС фірми Xilinx представлені в таблиці 5, а в ПЛІС інших фірм – в таблиці 6.

Таблиця 5. Основні технічні характеристики мікропроцесора при його реалізації в ПЛІС фірми Xilinx.

| Серія ПЛІС Xilinx | Апаратні витрати, ЕКЛБ | Максимальна тактова частота, МГц |

| Virtex | 190 | 60 |

| VirtexE | 190 | 77 |

| Virtex2 | 194 | 102 |

| Spartan3 | 194 | 45 |

Таблиця 6. Основні технічні характеристики в ПЛІС інших фірм.

| Фірма і серія ПЛІС | Апаратні витрати логічних комірок | Максимальна тактова частота, МГц |

| Actel ACT3 | 1874 | 18 |

| Altera Apex 20KE | 548 | 52 |

| Altera Stratix GX | 717 | 98 |

| Lattice ORCA4 | 304 | 16 |

Аналіз цих таблиць показує, що при реалізації мікропроцесора в ПЛІС фірми Xilinх досягається максимальна тактова частота і мінімальні апаратні витрати. При цьому приймалось до уваги, що за складністю приблизно 23 логічних комірки фірми Altera еквівалентні 10 ЕКЛБ. Слід відмітити, що проект мікропроцесора конфігурується без змін (крім модулів пам’яті) в ПЛІС будь-якої серії.

8. Можливості по зміні архітектури мікропроцесора.

Завдяки настроюванню архітектури мікропроцесора під користувацьку задачу можна зменшити апаратні витрати і підвищити швидкодію мікропроцесора. Тому проект даного мікропроцесора слід виконати з можливістю настроювання в широких межах.

Так, система команд і структура АЛП дозволяють додати в перелік команд нові команди. Це такі команди, як логічні функції, команди арифметичного і циклічного зсуву на один або декілька розрядів, команда пошуку старшої значущої одиниці, множення, ділення, команди завантаження констант, байтів з розповсюдженням знаку тощо. При зміні блоку РС можна програмувати глибину стека, додати до системи команд інші умови переходу, додати команду читання констант з області пам’яті програм, вставити лічильник ітерацій для апаратної підтримки програмних циклів і збільшити об’єм стека для зберігання стану цього лічильника при викликах підпрограм.

При зміні блоку регістрової пам’яті можна виконати цю пам’ять з двох сторінок і перемикати сторінки при відпрацюванні переривань, завдяки чому можна збільшити швидкодію за рахунок автоматичного збереження стану регістрової пам’яті; додати схему уповільнення активності процесора з метою енергозбереження; додати лічильник для слідкування за активністю мікропроцесора для підвищення його надійності.

Слід відмітити, що блоки BlockRAM мають 2 незалежні порти доступу. Один з цих портів може бути використаним для початкового завантаження PRAM з зовнішнього ОЗП. Також в такому PRAM може бути організована оверлейна структура програми, для чого додатковий блок прямого доступу до пам’яті повинен підвантажувати фрагменти програми з зовнішнього ОЗП на фоні виконання програми. При складнішій организації керування можна PRAM реалізувати у вигляді кеш-пам’яті, причому у випадку непопадання в кеш-пам’ять, процесор повинен зупинятися, а автомат керування кеш-пам’яттю повинен переписувати відсутні рядки з зовнішнього ОЗП.

При більш складній модернізації до ядра мікропроцесора додаються спеціалізовані конфігуровані обчислювальні блоки для виконання деяких функцій, що потребують високої продуктивності для свого виконання – апаратні прискорювачі. При цьому керування таким блоком може бути як за спеціальною командою, так і шляхом запису керуючої інформації в регістри, що знаходяться в адресному просторі периферійних пристроїв. Деякі складні команди можуть виконуватись в блоці прискорювача, тоді адреси даних надходять з ядра мікропроцесора таким самим чином, як при виконанні команд запису даних в ОЗП. Під час виконання функції дані можуть надходити паралельно з двох портів блоку DRAM.

При виконанні складного періодичного алгоритму адресація блоку DRAM може відбуватися за допомогою спеціального генератора адрес блоку прискорювача для організації конвеєрної обробки. При цьому для спрощення керування процесором його ядро гальмується.

Слід відмітити, що в ПЛІС, наприклад, Virtex2, широко застосовуються апаратні блоки множення, причому один блок множення припадає на 180–250 ЕКЛБ. Тому в мікропроцесорі RISC_ST є сенс використовувати команди множення, які реалізуються на таких блоках. Ці блоки також ефективно використовувати в блоці апаратного прискорювача.

При зміні архітектури мікропроцесора його апаратні витрати можуть змінюватись в межах 190–500 ЕКЛБ. Тоді, якщо в його структурі буде використано 1 або 2 блоки множення, апаратні ресурси ПЛІС будуть використані найбільш ефективно. З цієї точки зору обчислювальні заготовки мікропроцесорів іншої архітектури мають той недолік, що через те, що їхні апаратні витрати перевищують 500 ЕКЛБ і іноді досягають 3-4 тисячі ЕКЛБ, ресурси блоків множення ПЛІС використовуються нераціонально.

Обчислювальний модуль 16-розрядного RISC- мікропроцесора. (zip – файл)