Стилі написання програм на VHDL

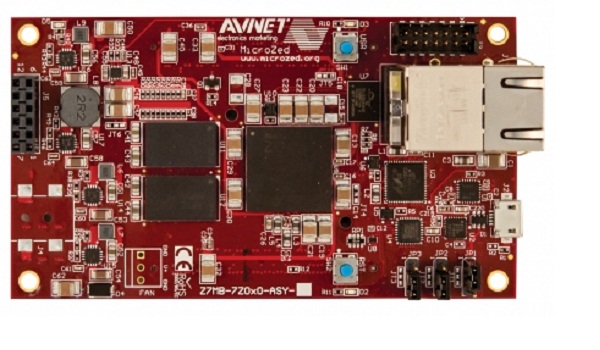

Стилі написання програм на VHDL дослідив Адам Тейлор, головний інженер фірми Electrical Systems at E2V, який раніше був керівником розробок у провідній європейській компанії Astrium, яка займалась розробкою космічних телекомунікаційних процесорів на базі замовлених НВІС та ПЛІС Virtex 5 QV. У Інтернеті він відомий як автор серії заміток та відповідної книги MicroZed Chronicles про досвід програмування плати Avnet MicroZed на базі ПЛІС Xilinx Zynq (на фото).

(http://www.electronics-eetimes.com/sites/default/files/documents/whitepapers/1-edn-pdfarticles/download-pdf-1606-feat-e2v.pdf )

Є кілька стилів написання VHDL-кодів. Основна відмінність між ними в тому, як виділяються ключові слова.

За першим стилем, весь текст складається з малих літер.

За другим стилем ключові слова набирають малими літерами, а решту, включаючи назви типів, бібліотек — великими, як це зроблено у довіднику з VHDL (VHDL Language Reference Manual).

За третім стилем — навпаки — ключові слова набирають великими літерами, а решту — малими.

Головним аргументом того, що ключові слова слід виділяти висотою букв є те, що це допомагає інженерам та тестувальникам їх швидко знаходити та розпізнавати як синтаксичні одиниці.

Але у наш час поширені редактори текстів програм, які розпізнають синтаксис та підсвічують кольором ключові слова. Якщо у такому редакторі читати VHDL-тексти, які написані трьома вказаними стилями, то не вдається віддати перевагу одному з цих стилів. Отже, притримування певного стиля втрачає смисл і є необов’язковим.

Хоча такі нові редактори є доволі ефективними, не слід забувати, що деякі користувачі не розрізняють кольорів, а деякі з членів команди розробників користуються звичайним редактором чи читають текст з чорно-білого аркуша.

Багато компаній впроваджують свій власний стиль кодування. Такий стиль приймає до уваги наступні особливості завдання сигналів.

— Узгодження імен синхросигналів, наприклад, ім’я сигналу включає значення його частоти: clk_40MHz.

— Узгодження імен сигналів початкового встановлення (активна одиниця чи активний нуль) та їх положення відносно синхросигналу ( близьке положення сигналу асинхронного скидання до фронту синхросигналу може призвести до попадання до метастабільного стану).

— Узгодження імен сигналів, наприклад, сигналів дозволу, які мають нульовий активний рівень. Таке ім’я часто має суфікс типу _n або _z . Наприклад, RAM_CS_n.

— Задається конкретна множина бібліотек, які дозволено використовувати. Наприклад, у сучасному проекті дозволяється бібліотека std_logic_1164, як обов’язкова, numeric_std, як бібліотека арифметичних функцій і не дозволяється аналогічна бібліотека std_arith, як застаріла. А бібліотеки text_io, math_real дозволені лише для стендів для іспитів.

— Регламентується використання типу std_logic та std_ulogic для певного роду сигналів та портів (std_logic — це тип std_ulogіс, для якого визначена функція вирішення конфлікту у випадку, коли сигналу виконується присвоювання у кількох паралельних операторах).

— Визначаються дозволені режими портів. Багато компаній вимагають використання лише режимів in, out та inout (лише для двонаправлених шин) та забороняють використання buffer. Також більшість компаній регламентують типи портів лише std_logic чи std_logic_vector щоб простіше стикувати модулі від різних розробників, особливо у великому колективі.

— Як правило, якщо проект стосується критичного застосування, то регламентується використання змінних у процесах.