Фільтри зі скінченною характеристикою з мінімізованими апаратними витратами

УДК 004.383

Анатолій Сергієнко, Кадір Сафван Хусейн, Анастасія Сергієнко

Anatoliy Sergiyenko, Quadir Safwan Husein, Anastasia Serhienko

Minimized hardware FIR Filter Design

Розглядається розробка паралельних нерекурсивних фільтрів, які реалізуються в програмованих логічних інтегральних схемах. Новий метод полягає в тому, що блоки множення на коефіцієнти, які мають невелику амплітуду, заміняються на блоки постійної пам’яті, які зберігають кратні значення цих коефіцієнтів. За рахунок цього зменшуються апаратні витрати на реалізацію фільтра та збільшується його пропускна спроможність.

Ключові слова: ПЛІС, нерекурсивний фільтр, конвеєр .

The development of the parallel finite impulse response filters for the FPGA implementation is considered. A new method consists in substituting the multipliers to the small coefficients to the constant coefficient multipliers, which store the multiplied values of these coefficients. Due to this, the filter hardware volume is minimized and its throughput is increased.

Key words: FPGA, FIR filter, pipeline.

Вступ. Програмовані логічні інтегральні схеми (ПЛІС) широко використовуються для високошвидкісної обробки цифрових сигналів. Архітектура ПЛІС адаптована до реалізації фільтрів зі скінченною імпульсною характеристикою (СІХ). Для цього, наприклад, ПЛІС фірми Xilinx містять блоки DSP48, кожен з яких призначений для розрахунку одного ступеня СІХ-фільтра в конвеєрному режимі. Але порядок такого фільтра обмежений об’ємом ПЛІС та кількістю блоків DSP48 в одному стовпці елементів мікросхеми. Як результат, порядок СІХ-фільтра, який генерується утилітою Xilinx Coregen для ПЛІС Spartan-6, обмежена діапазоном від 8 до 48 [1]. Крім того, якщо ПЛІС використовується лише для фільтрації, то в ній неефективного використовується решта програмованих ресурсів, таких як конфігуровані логічні блоки та їх логічні таблиці (ЛТ).

Існує багато методів реалізації СІХ-фільтрів, які не мають блоків множення. Більшість із них використовують схеми множення на константу (СМК), які мають мінімізований об’єм апаратного забезпечення. Вони широко використовуються у ПЛІС протягом десятиліть. При цьому такі фільтри зовсім не застосовують апаратні блоки множення, які входят у склад блоків DSP48 [2,3,4].

У роботі запропоновано новий підхід до розробки СІХ-фільтру, який використовує як апаратні блоки множення, так і СМК. Він забезпечує як збільшення порядку фільтра, так і мінімізовані апаратні витрати, а також підтримує високу пропускну здатність фільтра.

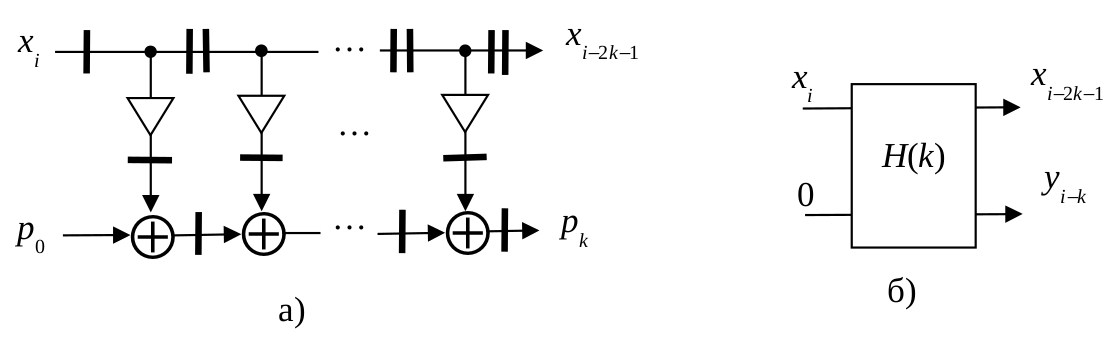

Структура СІХ-фільтра. СІХ-фільтр, якиф призначений для реалізації у ПЛІС фірми Xilinx FPGA, має відому систолічну структуру [1]. Граф синхронних потоків даних (ГСПД) систолічної структури фільтра k-го порядку показана на рис.1, а його умовне зображення — на рис.1, б. Тут xi, yi є вхідними та вихідними даними, кола, трикутники та товсті відрізки представляють собою додавання, множення на коефіцієнт і затримку на один такт, відповідно. Цей граф відображається у відповідну паралельну конвеєрну структуру з максимальною тактовою частотою за допомогою відображення один до одного.

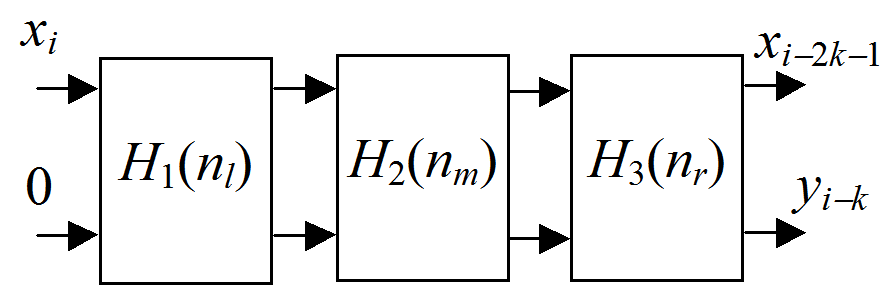

Набір коефіцієнтів СІХ-фільтра n-го порядку формує його імпульсну характеристику H(n). Пропонується реалізувати СІХ-фільтр з трьох блоків, які обчислюють згортку з лівою H1(nl), середнєю H2(nm) та правою H3(nr) підмножинами коефіцієнтів, n = nl + nm + nr . Відповідний модернізований ГСПД показано на рис.2. У більшості випадків розрядність коефіцієнтів H1(nl) та H3(nr) набагато менше, ніж коефіцієнтів H2(nm). Тому бажано реалізувати частину фільтра, позначену на рис.2 як H2(nm), використовуючи блоки DSP48, а решту фільтра —з використанням СМК.

Третій блок фільтра, який стоїть останнім у графі на рис.2, повинен мати підвищену розрядність проміжних результатів, щоб зберегти низький рівень помилок від їх усікання. Це може суттєво знизити ефективність фільтра, оскільки багаторозрядний суматор на основі ЛТ є значно повільнішим, ніж відповідний суматор у блоці DSP48.

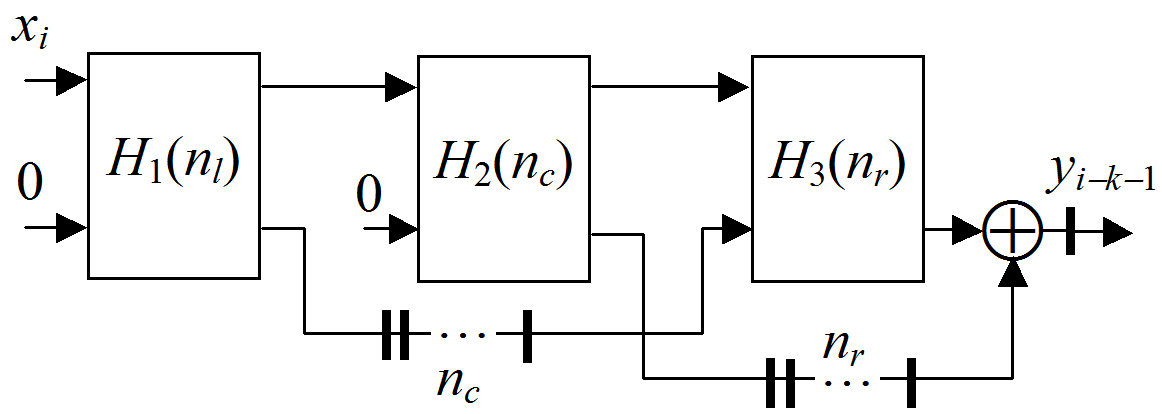

Щоб звести до мінімуму цей фактор, запропоновано удосконалений ГСПД, який показано на рис.3. Відповідний удосконалений фільтр містить дві частини H1(nl) та H3(nr) з однаковою розрядністю, яка набагато менша, ніж розрядність операндів блоку DSP48. Результат фільтрації формується в окремому суматорі зі збільшеною розрядністю. Як результат, розроблений СІХ-фільтр містить лише nm блоків DSP48, яких може бути набагато менше, ніж порядок фільтра n.

Експериментальні результати. Для оцінки ефективності НІХ-фільтрів з запропонованою структурою, було випробувано три реалізації фільтрів нижніх частот порядку n = 35, коефіцієнти, вхідні та вихідні дані яких мають розрядність 16. При цьому СМК були побудовані з використанням представлення коефіцієнтів у канонічній двійковій системі числення [4], причому дерево суматорів СМК має не більше п’яти вхідних складових. За цими умовами, перший та третій блоки фільтрів (див. рис. 2, 3) мають як мінімізовані апаратні витрати, так і високу пропускну здатність.

ГСПД, представлені на рис. 1-3 були описані мовою VHDL. Потім проекти фільтрів були синтезовані для ПЛІС Xilinx Spartan-6. Результати синтезу для деяких фільтрів низьких частот показані в таблиці 1. Щоб визначити інтегральну характеристику апаратних витрат Q, вважалося, що для реалізації 18-розрядного блоку множення, що входить у склад блоку DSP48, потрібно 200 ЛТ.

Таблиця 1. Прараметри СІХ-фільтрів

| Структура фільтра | Апаратні витрати | Максимальна частота fC, MГц | fC/Q | |||

| ЛТ | тригерів | DSP48 | Q | |||

| Систолічна, рис.1 | 0 | 0 | 33 | 33 | 390 | 11.8 |

| Модернізована, рис.2 | 772 | 1538 | 17 | 20.9 | 146 | 7.0 |

| Удосконалена, рис.3 | 914 | 1639 | 17 | 21.6 | 267 | 12.4 |

Аналіз таблиці показує, що структура фільтра на базі лише блоків DSP48 забезпечує максимальну тактову частоту дискретизації fC за рахунок збільшених еквівалентних апаратних витрат Q. Модернізована структура має меншу величину fC, але забезпечує мінімальний обсяг апаратного забезпечення. І удосконалена структура має менші апаратні витрати ніж систолічна, а її відношення пропускної здатності до апаратурних витрат fC /Q досягає максимуму.

Висновки. Запропоновано модернізацію та удосконалення систолічної структури цифрового фільтра зі скінченною імпульсною характеристикою, яка реалізована у ПЛІС. Модернізація полягає в тому, що в структурі використовуються як універсальні апаратні блоки множення, так і блоки монження на коефіцієнт, які реалізовані на основі суматорів. Нова структура фільрів забезпечує як оптимальне відношення пропускної здатності до апаратних витрат, так і збільшення максимального порядку реалізованих фільтрів. Одержані фільтри описані мовою VHDL і мають приблизно удвічі менше число блоків множення, ніж фільтри, які згенеровані программою Xilinx Coregen.

Список використаних джерел

- Spartan-6 FPGA DSP48A1 Slice User Guide. UG389 (v1.2) / Xilinx Inc. / May 29, 2014. —46 p.

- Meyer-Baese. U. Digital Signal Processing with Field Programmable Gate Arrays. Springer, 4-th Ed. 2014. — 930 p.

- Sergyienko A. FIR filter soft core generator / A. Sergyienko, V. Vasylienko, O. Maslennikow // Prace IV Konferencji Krajowej „Reprogramowalne uklady cyfrowe”, RUC’2001. –Szczecin, Poland. 2001. —Р. 167-172.

- Kumm M. Multiple Constant Multiplication Optimizations for Field Programmable Gate Arrays. Springer, 2016. — 206 p.